范文一:行业资料四位二进制8421bcd码加法器

设计题目: 四位二进制8421BCD码加法器

学 院: 理学院

专 业: 09电子信息科学与技术

班 级: 1班

学 号: 200931120102; 200931120103;

200931120105

姓 名: 陈俊宇 陈明源 邓坤勇

电子邮件: 1205335255@qq.com

时 间: 2011年12月8日

成 绩:

指导教师: 刘丹

华 南 农 业 大 学

理 学 院 应 用 物 理 系

课 程 设 计(报告)任 务 书

题目 四位二进制加法器

任务与要求:

运用电子器件和一些IC芯片设计一个四位二进制

8421BCD码加法器。用以实现两个四位二进制数8421BCD

码的加法通过数码管显示相加所得的两位十进制数。用八

个开关的开闭控制电平的高低,用高电平表示1;用低电

平表示0。将输入的高电平接入74LS283加法器进行运算。

得到的结果,分别将高低位输入74LS248译码器输出到两

个七段数码管。由数码管显示加法结果得到的BCD码。学

会数字信号芯片的原理和在实际中的应用。

开始时间:2011年12月1日;结束时间:2011年12月

13日

四位二进制8421BCD码加法器

学生:陈俊宇,陈明源,邓坤勇;指导老师:刘丹

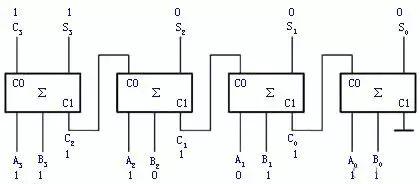

摘要:本设计通过八个开关将A3,A2,A1,A0和B3,B2,B1,B0信号作为加数和被

加数输入四位串行进位加法器相加,将输出信号S3,S2,S1,S0和向高位的进位

C3各自分别通过一个 74LS248译码器,最后分别通过数码管实现二位BCD码显

示。

关键词:加法器,译码器,数码管,,,,码显示。

Abstract: the design through eight switch will A3, A2, A1, A0 and B3, B2, B1, B0 signal as addend and BeiJiaShu input four serial carry adder addition, will output signal S3, S2, S1, to carry high and S0 C3 their respective through a 74 LS248 decoder, finally, through the digital tube realize two BCD display.

Keywords: adder, decoder, digital tube, BCD display

总体方案论证和选择

设计思路:两个四位二进制数的输入可用八个开关实现,这两个二进制数经全加器求和后最多可以是五位二进制数。本题又要求用两个数码管分别显示求和结果的十进制十位和各位,因此需要两个译码器分别译码十位和个位。而两个译码器可以选择74LS248作为译码输出。

加法器的选择:

全加器:能对两个1位二进制数进行相加并考虑低位来的进位,即相当于3个1位二进制数相加,求得和及进位的逻辑电路称为全加器。

1) 串行进位加法器

构成:把n位全加器串联起来,低位全加器的进位输出连接到相邻的高

位全加器的进位输入。

优点:电路比较简单。

最大缺点:进位信号是由低位向高位逐级传递的,运算速度慢。

2) 超前进位加法器

为了提高运算速度,必须设法减小或消除由于进位信号逐级传递所消耗

的时间,于是制成了超前进位加法器。

优点:与串行进位加法器相比,(特别是位数比较大的时候)超前进位

加法器的延迟时间大大缩短了。

缺点:电路比较复杂。

综上所述,由于此处位数为4(比较小),出于简单起见,这里选择串行进位加法器。有由于有现成的四位二进制加法器74283,而且74283是基于串行进位加法器制作的,所以采用两块74283和一些与门和非门构成一个8421BCD码加法器。

译码器的选择:

译码是编码的逆过程,将输入的每个二进制代码赋予的含意“翻译”过来,

给出相应的输出信号。译码器是使用比较广泛的器材之一,主要分为:变量译码器和码制译码器,其中二进制译码器、二-十进制译码器和显示译码器三种最典型,使用十分广泛。显示译码器又分为七段译码器和八段译码器,此处选择七段译码器。综上所述,最终选择74LS248译码器 数码管选择:

此处选七段发光二极管(LED)显示器,LED数码管要显示BCD码所表示的十进制数字就需要有一个专门的译码器,该译码器不但要有译码功能,还要有相当的驱动能力。上述选取了74LS248译码器,为了与该译码器配用,因此选取七段数码管。

总体设计

原理框图:原理框图如图1所示。

进位译码

器 加法器

低位译码

器

图1:原理框图

总的电路原理图:总的电路原理图如图2所示。

图2:总的电路原理图

说明:通过八个开关将A3,A2,A1,A0和B3,B2,B1,B0信号作为加数和被加数输入四位串行进位加法器相加,将输出信号S3,S2,S1,S0和向高位的进位C3通过译码器译码,再将输出的Y3,Y2,Y1,Y0和X3,X2,X1,X0各自分别通过数码管实现二位显示。

单元设计

加法器单元:

本四位二进制8421BCD码加法器采用的是两个四位二进制加法器74283和一些与门和非门构成的。其原理框图如图3所示。

译码器单元:

74LS248的动能表

七段显示译码器的主要功能是把“8421”二-十进制代码译成对应于数码管的七字段信号,驱动数码管,显示出相应的十进制数码。 数码管显示单元:

半导体七段显示器分为共阴极接法和共阳极接法两种,此处为了与74LS248译码器配套选用共阳极数码管。

课程设计所需元件:本课程需要的电子元件如下所示。

四位二进制加法器74LS283:2个 译码器74LS248:2个

与门74LS08:1个

非门74LS04:1个

160Ω电阻:22个

数码管:2个

总的实物电路图

心得体会

通过本次课程设计,我们加深了对所学知识的理解,并对某些知识进行了很好地应用,如8421BCD码加法器的设计等。同时,我们也更加强化了自己查阅资料的能力,这有助于提高我们的自学能力,整个过程中我还有请教老师和同学。总之,本次课程设计更加激发了我的学习欲望,有利于我们后续课程的学习。

当然,在这次课设中,我也遇到了不少问题,如对于六引脚的开关的处理,开始我们想当然地以为这六个引脚就是随便接着两边就可以实现电路的开关功能。而事实是我们错了,最后我请教了老师,才明白为什么错在了什么地方。但一波未平一波又起,在我们了解了开关的性能后又遇到了一个关于开关打开和闭合都是高电平的问题。实践证明模拟仿真与实际电路是有些差异的。最后采取了老师的建议,总算解决了这些问题,成功地将电路弄了出来。那一刻,我们真的很高兴。

总之,这次课设让我收获不少。

参考文献

【1】 数字逻辑电路与系统设计;蒋立平主编 电子工业出版社 【2】 Wenku.baidu.com 四位二进制加法器

【3】 电子技术 李春茂 主编 科学技术文献出版社

范文二:BCD码加法器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all; entity bcd is

port (a,b:in std_logic_vector(3 downto 0);

y:out std_logic_vector(4 downto 0)); end bcd;

architecture bh of bcd is

signal f:std_logic_vector(4 downto 0); signal m:std_logic_vector(4 downto 0); signal n:std_logic_vector(4 downto 0); begin

m<='0'&a;>

n<='0'&b;>

f<=m+n;>

y<=f when="" f<"01010"="" else="" f+"00110"="" when="">

"00000";

end bh;

(2)library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all; entity eda is

port(

clk:in std_logic;

q:buffer std_logic_vector(3 downto 0);

reset:in std_logic);

end eda;

architecture art of eda is

begin

process(clk,reset,q)

begin

if reset='1' then

q<="0000";>

elsif clk'event and clk='1' then q<>

end if ;

end process;

end art;

范文三:一位十进制BCD码加法器设计

一位十进制BCD码加法器设计

2012年3月30日

实验目的: 熟悉基于EDA平台的电路设计,掌握MAXPLUS的使用,并运用

MAXPLUS设计电路图,模拟其工作环境

实验原理: MAXPLUS软件能够模拟电路工作的实际情况,给电路设计带来方

便

实验内容:使用MAXPLUS设计一位十进制BCD码的加法器

部件的逻辑原理图:

一位全加器FA的逻辑图:

实验电路

图:

图三:

波形图:

实验步骤:分析一位BCD码进行加分运算的情况,进位或者不进位分成两种情

况,而进位又分为两种情况:

1) 若不进位,则结果直接相加即若仅为信号为0,则不进行其他

操作

2) 若进位,则要进行分析,BCD码只能表示0~9之间的数字,若超过9则

要进行进位,而当BCD码之和超过15(16~18)超过四位二进制的表示

范围,也要进行进位考虑

1?当和的范围是10~15时:画卡洛图得到的表达式是F=SS?S+SS依010,3Z

据表达式得到电路图添加到上图中,表达式的逻辑图如图三,当二者和

超过10时,例如当和为12时,二进制表示:1100,对其加6修正,修

正后结果是1(溢出)0010

?当和的范围超过了16时,超过四位二进制的表示范围,这需要对结

果进行修正,例如:二者和超过17时,二进制结果是1(溢出)0001,

对结果进行修正,这结果是1(溢出)0111,若对结果修正,也要对结

果加0110

实验的测试数据及测试结果:

AAAA BBBB S’S’S’S’ C’ 3210 3210 32103

0100 0101 1001 0

0110 0110 0010 1

1000 1000 0110 1

实验小结:用BCD码表示的十进制加法要对其进行详细分析:

? 当二者和小于等于9时,无需进位,不用进行其他的任何处理,直接进行

加法运算;

? 当和大于等于10小于等于15时,要对其进行加6修正(+0110)

? 当合大于等于16时,超过了四位二进制的表时范围对于其结果也要进行

加6修正,由于?、?的情况不能同时发生,因此二者的信号不能合并 实验中遇到的问题及解决方法 :

? 判断冗余位:1010、1011、1100、1101、1110、1111是冗余位,用卡洛

图,

判断,卡洛图

SS SS 00 01 11 10 3210

00 0 0 1 0

01 0 0 1 0

11 0 0 1 1

10 0 0 1 1 得到了表达式:F=SS?S+SS010 3Z

? 当和大于等于16时超出四位二进制表示范围,不可能存在冗余位,从而

当和大于16时要进行另外的处理

实验过程中对波形图文件的编辑还不够熟练,很难正确的画出满足仿真所需要的波形

心得体会:通过这此的实验设计大致明白了如何用MAXPLUS,绘制电路图,但是对于电路的仿真多少还是有一些问题,可能是软件的兼容问题,或许下次可以使用其他的仿真软件,同时我也了解了如何去设计加法器,同时对于BCD码也有了进一步的了解

范文四:实验二 一位8421BCD码加法器的设计

实验二 一位8421BCD码加法器的设计 一、实验目的

1. 理解四位加法器7483和四位比较器7485的工作原理及使用 2. 掌握一位8421BCD码加法器的工作过程

3. 进一步熟悉Quartus软件的使用,了解设计的全过程, 二、实验内容

1. 采用画原理图的方法设计一位8421BCD码加法器。要求使用四位

加法器7483和四位比较器7485及必要的逻辑门电路。 三、分析过程

7483是四位二进制加法器,其进位规则是逢16进1。而8421BCD码表示的是十进制数,进位规则是逢10进1。用7483将两个1位BCD码相加时,当和小于等于9时,结果正确;当和大于9时,需加6进行修正。

实验中要求使用7483、7485及必要的逻辑门完成。由于7483通过输出引脚C4 S3 S2 S1 S0输出二进制的和,7485是四位比较器,关键在于如何通过7483及7485的输出判断何时应对结果修正以及如何修正。

由于两个1位十进制数相加时,和的取值范围是0—18,将该范围内各数值对应的二进制数和8421BCD码列表,以便寻找何时应对结果修正以及如何修正

十进二进制数 十进制数 备注 制 C4 S3 S2 S1 S0 DC D3 D2 D1 D0

不需修0 0 0 0 0 0 0 0 0 0 0

正 1 0 0 0 0 1 0 0 0 0 1

2 0 0 0 1 0 0 0 0 1 0

3 0 0 0 1 1 0 0 0 1 1

4 0 0 1 0 0 0 0 1 0 0

5 0 0 1 0 1 0 0 1 0 1

6 0 0 1 1 0 0 0 1 1 0

7 0 0 1 1 1 0 0 1 1 1

8 0 1 0 0 0 0 1 0 0 0

9 0 1 0 0 1 0 1 0 0 1

10 0 1 0 1 0 1 0 0 0 0

需要修11 0 1 0 1 1 1 0 0 0 1

正 12 0 1 1 0 0 1 0 0 1 0

13 0 1 1 0 1 1 0 0 1 1

14 0 1 1 1 0 1 0 1 0 0

15 0 1 1 1 1 1 0 1 0 1

16 1 0 0 0 0 1 0 1 1 0

17 1 0 0 0 1 1 0 1 1 1

18 1 0 0 1 0 1 1 0 0 0

从表中分析可得出如下结论:

当7483输出的二进制数的和为0---9时,即S3 S2 S1 S0? 9时结果正确,不需修正;当和为10-----15时 S3 S2 S1 S0, 9时,需加6修正,此种情况可将7483的输出S3 S2 S1 S0送入7485的输入引脚A3 A2 A1 A0,将1001(即9)送入7485另一组输入引脚B3 B2 B1 B0,若7485的输出A,B=1,则说明需加6修正;当和为16、17、18时,结果需加6修正。此种情况7483的输出S3 S2 S1 S0,9,但C4=1。

综合以上分析,当7483输出的二进制数的和S3 S2 S1 S0, 9或C4=1时结果需修正。此修正的条件可通过7485的输出A,B和7483

OR1)获得。当OR1输出为1时需修正,当输出的C4通过逻辑或门(

OR1输出为0时不需修正。(分析出何时应对结果修正)

需再使用一片7483实现加6修正,将第一片7483输出的二进制数的和S3 S2 S1 S0送入第二片7483的输入引脚A3 A2 A1 A0,第二片7483的输入引脚B3 B2 B1 B0接入0、OR1输出、OR1输出、0。由于不需修正时,OR1输出为0,需修正时OR1输出为1,实现加6修正。(分析了如何实现修正)

分析BCD码十位获得,当第一片7483输出的二进制数的和为0—16时,BCD码十位由第二片7483输出的C4获得,当第一片7483输出的二进制数的和为16、17、18时,BCD码十位由第一片7483输出的C4获得。因此,BCD码十位由两片7483的C4经过逻辑或门(OR2)获得。

四、原理图(粘贴QUARTUS中绘制的原理图)

五、功能仿真的波形图及说明(包含不需修正以及修正的情况)

六、实验体会与收获

说明发现问题以及解决的方法

范文五:一位加法器

实验一 1位全加器电路的设计

一、实验目的

1、学会利用Quartus Ⅱ软件的原理图输入方法设计简单的逻辑电路;

2、熟悉利用Quartus Ⅱ软件对设计电路进行仿真的方法;

二、实验内容

设计一个由1位全加器,并进行编译与仿真。

三、实验仪器

Quartus II软件

四、实验步骤

1. 使用Quartus 建立工程项目

打开Quartus 软件,界面如图1-1示。

图1-1 Quartus软件界面

在图1-1中从【File 】>>【New Project Wizard... 】新建工程项目,出现新建项目向导New Project Wizard 对话框。该对话框说明新建工程应该完成的工作。点击

进入新建项目目录、项目名称和顶层实体对话框。输入项目目录、工程项目名称和顶层实体名同为fadder 。

这里是新建工程,暂无输入文件,直接点击, ,继续直接点击进入工程信息报告对话框如图1-7

2、新建VHDL 文件。

从【File 】>>【New. 】打开新建文件对话框。选择DesignFile/VHDL,

按钮。 输入源程序:

图 2-1 vhdl语言输入

3、 编译

选择【Processing 】>>【Compile 】进行编译。若有错误,根据信息窗口提示找出并更正错误,直至编译成功为止。

选择【Processing 】>>【Netlist 】>>【RTL 】

图3-1 编译成功窗口

4、创建vw 文件,并仿真

点击新建按钮【New 】>>【V erfic 】>>【Vector Waveform File】,出现仿真文件编辑界面。

图4-1仿真编辑窗口

选择【Edit 】>>【End time】出现设置仿真时间长度对话框。

在Name 下方空白区域右击出现操作菜单,选择Insert Node or Bus ,弹出添加节点或总线对话框如图1-25所示,

图4-2 添加节点或总线对话框

选择Node Finder 出现查找节点对话框。在Filter 栏中选择Pins:all,在Look in 栏中选择Fadder ,点击List

再点击

图4-3 节点查找对话框

分别选择节点a,b,c ,利用波形编辑按钮设置节点的输入波形如图,并保存波形文件为fadder.vwf 。

图4-4 添加节点后的波形编辑窗口

选择【Assignments 】>>【Setting 】在弹出窗口的Category 下单击Simultor setting ,出现Simultor setting 对话框,在Simultor input 栏中设置仿真文件路径指向fadder.vwf 如图1-30所示,单击OK 结束设置。

图4-5仿真波形设置

选择【Processing 】>>【Start simulation】或用快捷按钮进行波形仿真。仿真成功后,生成全加器的仿真波形如图1-31所示

图4-6全加器的仿真波形

五、实验代码

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity adder1 is

port (a,b,ci:in std_logic;

s,co:out std_logic);

end adder1;

architecture func of adder1 is

signal x,y:std_logic;

begin

x<=a xor="">

y<=x and="">

s<=x xor="">

co<=y or="" (a="" and="">

end func;

六、实验小结

接触Quartus II的第一天,也是第一次接触VHDL 语言,刚开始有点不知如何下手,操作起来也不够熟练。然后上网查找资料和教程, 另外请教同学, 让我感觉收获很多。 现在我知道了Altera Quartus II 作为一种可编程逻辑的设计环境, 由于其强大的设计能力和直观易用的接口,越来越受到数字系统设计者的欢迎。

对于实验,我们首先理解他的原理,知道他的操作过程。另外, 多练习了几遍软件的操作, 也让我感觉熟练了很多。

最后,在此,谢谢老师的耐心教导,同学的帮助!

转载请注明出处范文大全网 » 行业资料四位二进制8421b

任七控

任七控