范文一:自对准硅化物工艺研究

第 34 卷第 6 期 134, ? 6 微 电 子 学 V o l

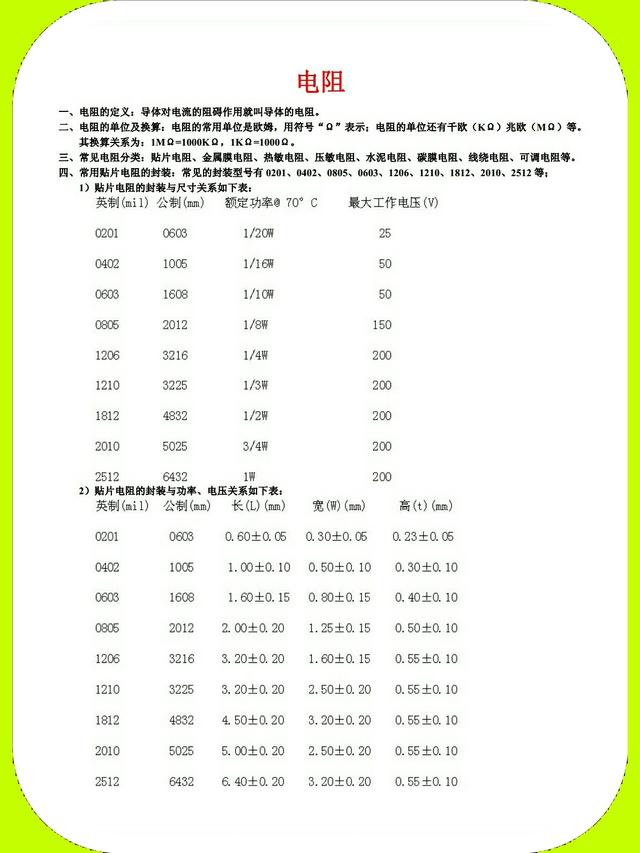

2004 年 1 2 月 12004D ec M icroelectron ics

() 文章编号: 100423365 20040620631205

自对准硅化物工艺研究 1, 2 1 2王大海, 万春明, 徐秋霞

()11 长春理工大学, 吉林 长春 130021; 21 中国科学院 微电子研究所, 北京 100029

摘 要: 对适用于深亚微米 器件的各种自对准硅化物工艺进行了讨论, 并对不同硅化物 CM O S

薄膜的特性进行了分析。结果表明, 随着大规模集成电路特征尺寸的不断缩减及其对器件性能要求 的不断提高, 常规 和 的自对准硅化物工艺已经不能满足器件特征尺寸进一步缩小的需要;T i Co 的自对准硅化物工艺可以很好地满足超深亚微米及纳米器件对硅化物的需求。 N i

关键词: 超深亚微米; 器件; 自对准硅化物; 纳米器件; 自对准硅化物 中图CM O S N i

+ 分类号: 304. 24 文献标识码: TN A

An In vest iga t ion in to D if feren t Sa l ic ide Process Technolog ie s

1, 2 1 22, 2, 2W AN G D aha iW AN Chunm ingXU Q iux ia

(11, , 130021Changchun U niversity of S cience and T echnology ChangchunJ ilin

21 , , , 100029, 1 1 )Institu te of M icroelectronicsT he Chinese A cad em y of S ciencesB eij ing P R China

22’: AbstractD ifferen t selfa ligned silicide techno logies fo r subm icron CM O S VL S Is have been investigated in2

1 1 , ten sivelyCharacteristics of differen t silicide film s have been analyzedIt has been show n thatw ith the ever

’, sh rink ing featu re size in VL S Is and the increasing dem and on device perfo rm ancesthe conven t io nal T i sicilide and

2, Co sicilide cou ld no longer m eet the requ irem en t fo r deep subm icron CM O S VL S I app licat io n sw h ile N i silicide

2 22, 2techno logy is app licab le fo r veryo r u lt radeep subm icron CM O S VL S Iand even nano dev ices by im p roving N iSi

1salicide p rocess

222: ; ; ; ; Key wordsU lt ra deep subm icronCM O S deviceSelfa ligned silicideN ano dev iceN i salicide

: 2520EEACCM

, 以防止多晶硅中杂质的挥发; 并且, 硅 的自钝化层

化物?掺杂多晶硅复合栅结构具有良好的工艺兼1 引 言

容 性, 保持了多晶硅与二氧化硅之间良好的界面,

因而 得到了广泛的研究。 在超大规模集成电路中, 随着电路规模的不断

随着工艺技术的不断进步, 1960 年代, 首次提 扩大和器件特征尺寸的不断减小, 互连线电阻对电

出将硅化物用于硅接触孔, 以降低因接触孔尺寸变 路性能的影响变得愈发重要。 重掺杂的多晶硅由于

小、表面活性杂质浓度降低而导致的接触电阻的增 自身杂质固溶度的限制, 使电路的 延迟时间变 RC

加。在这种情况下, 硅化物采用金属与硅衬底热反应 长, 从而限制了特征尺寸的进一步减小。为了克服这

的方法生成。 当器件尺寸进一步减小到深亚微米阶 一限制, 发展了低电阻率的难熔金属硅化物及其互

段时,寄生串联电阻成为器件性能进一步 M O SFET 连技术。金属硅化物最初应用到栅上有两种方法: 一

提高的障碍。寄生串联电阻主要由接触电 M O SFET 种是将金属硅化物直接用作栅互连材料, 替代重掺 [ 1, 3 ]阻、薄层电阻、电流扩展电阻和电流积累电阻 4 部分 杂多晶硅; 另一种是采用硅化物?掺杂多晶硅[ 829 ][ 4, 7 ]组成。 为了同时克服源?漏及多晶硅栅的接触合栅结构 () 。后者由于硅化物下面复 Po lycide

电 阻和薄层电阻对器件性能的影响, 硅化物自对的多 晶硅原子在高温氧化气氛中可以迅速穿过硅

准工 艺应运而生。 硅化物自对准工艺不仅同时降化物, 并在其表面形成氧化层, 从而比较容易形成

低了多 高质量

收稿日期: 2003210227; 定稿日期: 2003212215

; 当线宽< 011="" 时,="" 由于凝聚效应,="" 电阻不断升高晶硅和源λm="" ?漏区的薄层电阻和接触电阻,="">

使连线电阻进一步急剧升高。 能力, 而且简化了工艺。 目前, 和 的自对线 T i Co

准硅 化物工艺技术已经实现了量产化。但是, 随着薄膜的方块电阻可通过一个简单的模型 T iSi2 [ 11 ]寸的不断缩减, 常规的 和 自对准硅器件尺 T i Co 来计算。在线宽为 014 与较低的 相的晶 (54 Λm C

化物工艺 技术已经不能满足器件性能的要求。 此粒尺寸可以比较) 时, 认为 相的晶粒和 相 54 49 C C

时, 的自 N i 对准硅化物工艺也就应运而生。 的晶粒是串联起来的, 这是因为, 此时在线条上只有

本文重点讨论了适用于深亚微米 器件 相和 相的晶粒, 或者 相的晶粒完全占 54 49 54 CM O S C C C

据线条, 或者完全被 相的晶粒所占据; 在线宽 49 C 的各种 (、、自对准硅化物工艺; 对不同的硅 ) T iCoN i

大于 014 即大于较低的 相晶粒尺寸) 时(54 , Λm C 化物工艺及硅化物薄膜性能进行了对比和分析。

54 相的晶粒和 相的晶粒是并联起来的; 在线 49 C C

宽大于 10 即远远大于较低的 相晶粒尺寸) (54 Λm C 2 实 验

时, 在线条上只有 54 相的晶粒; 在线宽小于 011 C

(即远远小于较高的 49 相晶粒尺寸) 时, 在线条 Λm C 利用磁控管平面溅射台进行不同金属薄膜和不

上只有 相的晶粒。采用薄膜的电阻率对硅化物 49 C 同厚度的溅射。衬底为不同掺杂类型 (、、和不 ) A sBP

的薄膜电阻进行了理论计算, 并考虑到串连电阻要 同浓度的衬底硅片。 溅射后的样品通过快速热退火

大于并联电阻。 结果发现, 在线宽大于 012 时, Λm () 和选择性腐蚀进行硅化物自对准工艺; 并通 R TA

理论计算值和实验测量值非常吻合; 而在线宽小于 过透射电子显微镜 ()、电子衍射 ()、能量散 T EM ED

011 时, 实验值明显大于理论值。进一步的 Λm T EM 射 射线谱 ()、射线衍射) 等表征手 (X EDX XRD X

和 分析表明, 有两个方面的原因: 1) 薄膜 EDX T iSi2 段, 对样品进行了表征。

的热生长动力学表明, 原子是主动扩散源, 在 Si

薄膜的生长过程中, 多晶硅栅条上的 原子 T iSi2 Si 3 结果与讨论

一方面与多晶硅栅条上的 金属薄膜反应生成 T i 薄膜; 而在多晶硅栅条两侧的 原子有可能 T iSi2 Si 在深亚微米 器件中, 硅化物的电阻率、 CM O S 扩散到侧墙上, 与侧墙上的 金属薄膜反应生成 T i 耗硅量、热稳定性以及所形成硅化物浅结的漏电是 薄膜, 一方面使形成在多晶硅栅条上的 T iSi2 T iSi2 影响 器件性能的主要方面。下面从这几个方 CM O S 薄膜中间厚两边薄, 从而使 薄膜的有效厚度 T iSi2 面对 、、的自对准硅化物工艺进行讨论。T iCoN i 减小, 结果造成 薄膜的方块电阻升高; 另一方 T iSi2 311 不同硅化物薄膜的电阻率 [ 12 ] 面, 容易产生“桥连”和“空洞”现象, 即在侧墙上 31111 常规 薄膜的方块电阻与线宽的关系 T iSi2 也形成了硅化物薄膜和重掺杂多晶硅在水平方向上 随着线宽 () 的减小, 薄膜的方块电阻逐W T iSi2 的不连续。的分析也证实了这一点。2) 分 T EM EDX [ 10, 11 ]渐增大。 在?1 时, 薄膜的方块电 W Λm T iSi2 析表明, 硅化物薄膜晶粒间界区域的峰值比晶粒区 阻随线宽的减小稍有增加, 但基本上没有明显变化; 的小, 可能是由于此区域薄膜比较薄, 或此区域薄膜 在 1 ? ?012 时, 薄膜的方块电阻 Λm W Λm T iSi2 的密度比较低, 或此区域的硅化物薄膜形成不充分 随线宽的减小而明显增加; 在 ? 012 时, W Λm 而引起的, 结果造成 薄膜的方块电阻升高。考 T iSi2 薄膜的方块电阻随线宽的减小而急剧增加。T iSi2 虑以上两个因素, 在线宽小于 011 时, 理论计算 Λm 分析表明, 在 1 ? ?012 时, T EM Λm W Λm 值和实验值也比较吻合。 薄膜的方块电阻随线宽的减小而明显增加是 T iSi2 对于 和 掺杂的样品, 在线宽小于 011 B P Λm 由于高阻态的 49 相到低阻态的 54 相的不完全 C C 时, 薄膜的方块电阻的变化与掺杂的样品 T iSi2 A s 转变所致, 即除 相外, 还有 相的存在。 54 49 C C ED 基本一致; 在 1, 2 ? ?012 时, 薄 Λm W Λm T iSi2 分析表明, 大晶粒在 014 左右具有 结构; Λm T iSi2 膜的方块电阻的变化趋势与掺杂的样品基本A s 而小晶粒在 012 左右具有 结构。当 012 Λm ZrSi2 Λm 一 致, 只是其阈值线宽 (薄膜电阻开始增加T iSi2 ? ?011 时, 薄膜完全由高阻态的 49 W Λm T iSi2 C 时的 线宽) 有所不同。 掺杂的样品为 2 , P Λm A s 相组成。这是因为 54 相的成核发生在 3 个晶粒的 C 掺杂的 样品为 115 掺杂的样品为 1 。这, Λm B Λm交叉处, 所以, 当线宽< 012="" 时,="" 由于="" 相成核="" 54="" λm="" c="" 是由于衬="" 底的不同掺杂类型抑制了="" 的相变而t="" isi2="" 极其困难,="" 导致只有="" 高阻态相的存在,="" 使连线49="" c="">

, 尤其是对于 器件而言, 极其重要。31112 薄膜的方块电阻与退火温度和线宽的 更大的优势SO I N iSi [ 10, 13, 14 ] 关系

随着线宽的减小, 薄膜的方块电阻有明显 N iSi

减小的趋势。分析表明, 薄膜的晶粒尺寸 T EM N iSi

至少比 薄膜的晶粒尺寸小一半以上, 并且随 T iSi2

着线宽的减小, 晶粒有逐渐变大和侧向生长变厚的

“趋势”, 这显然有利于 薄膜方块电阻的减小。 N iSi

另外, 薄膜的热生长动力学表明, 原子是主 N iSi N i

动扩散源, 在 薄膜的生长过程中, 多晶硅栅条 N iSi

上的原子一方面与多晶硅栅条反应生成薄 N i N iSi

膜; 另一方面, 在侧墙上的 原子也可以扩散到多 N i

图 1 不同硅化物薄膜的耗硅量 晶硅栅条的两端, 与其反应生成 薄膜, 使在多 N iSi

313 不同硅化物薄膜的热稳定性 晶硅栅条上形成中间薄两边厚的薄膜, 从而增N iSi

在这三种硅化物中, 热稳定性最好的是 T iSi2

加薄膜的有效厚度, 相应地, 薄膜的方N iSi N iSi , 其次是 薄膜, 最后为薄膜。由于在薄膜Co Si2 N iSi 块

电阻也得到减小; 此举还大大降低了产生“桥连”和

薄膜的形成过程中有不同的相变过程, 只有温N iSi “空洞”的几率。 的分析也证实了这一点。 并 T EM 度范围在 400, 750 ?时才可以形成唯一的 C N iSi 且, 分析表明, 薄膜的晶粒间界区域的峰EDX N iSi 相; 而当温度高于 750 ?时, 会出现由相向高C N iSi

值和晶粒区的基本一样。 这表明, 形成的薄N iSi 电阻率的 N iSi2 相的转变, 从而引起薄膜方块电阻 膜

比较致密和均匀, 有利于 薄膜方块电阻的降N iSi 的增加。 目前, 改善薄膜热稳定性的方法主要N iSi 低。 有两种。一种是利用注入来改善薄膜的品N N iSi 2 对于不同的掺杂类型 (、、) , 薄膜的BPA sN iSi +

注入是在薄膜的溅射前进行的, 注入[ 16 ]+2 N i 质。N 方块电阻基本上没有太大的变化。 具体为: 在上层 后利用 对杂质进行激活。 分析表明, 注 R TA S IM S 金属薄膜的厚度大于 20 时, 不同掺杂类型的 N i nm + 入的主要分布在晶界的周围, 有助于改变 N N iSi 2 薄膜方块电阻基本上保持一致, 方块电阻在 2N iSi + 晶界的能量; 而且, 注入的也可以和或 反 N N i Si , 4 ??; 而当上层金属薄膜的厚度小于 20 2 8 N i nm 应生成氮化物而改变界面能, 从而抑制和延迟成团 时, 不同掺杂类型的薄膜方块电阻有微小的N iSi 效应 () , 提高 薄膜的热稳定性。 agg lom erat io nN iSi 变 化(掺杂的最大、次之、最小)。 因此, 随P A s B 另一种是利用 () 合金来改善 薄膜的品 N i P tN iSi 着N i 薄膜厚度的减小, 不同的衬底类型对硅化物[ 17 ]质。 由于的形成过程实际上是一个晶核控 N iSi2 阻的影响明显增强。造成这一现象的原因方块电 制过程, 当反应 (+ ?) 的自由能改变量N iSiSiN iSi2 是在不 N i 同的杂质中的扩散运动和所发生的反不能与界面能的增加量 (主要是由于新相物质 ?G 常规 薄膜的方块电阻与线宽应有所不同。 Co Si2 的形成 = + - ) 相平衡时, 这 ?ΡΡN iS i?S i ΡN iS i?N iS i ΡN iS i?S i 22的关系基本 上与薄膜的近似。 随着线宽的N iSi 种晶核控制反应便可以发生。 晶核的有效激活能 减小, 薄层电阻 (有所下降 在一定的温度和金属

薄膜厚度的情况 3 3 2

有下)。 在不同衬底掺杂类型的情况下, 薄膜的 Co Si2

方块电阻也没有明显的变化。

[ 15 ]312 不同硅化物薄膜的耗硅量

硅化物薄膜形成时所消耗的 量, 是衡量硅化 Si

物薄膜性能的重要参数, 它将直接影响硅化物浅结 的结深和漏电, 进而影响整个器件的性能。

图 1 给出不同硅化物薄膜 (、、) T iSi2Co Si2N iSi的耗硅量。从理论上讲, 每单位厚度的金属薄膜, Co 所消耗的硅最多, 次之, 最少, 分别为 3161 T i N i

()、21221 () 和 1183 ()。随着器件尺寸的不断 CoT iN i

缩小, 较少耗硅量的相对于 和 来讲, 具N i Co T i

正比于 。的掺杂有利于 ?的增加和?G ?Ρ ?G P t ?Ρ

3 的减小, 从而提高晶核的有效激活能 , 使?G ?G 成 核的数量下降, 降低 的形成几率, 从N iSi2

而提高 薄膜的热稳定性。N iSi

另外, 薄膜的方块电阻在温度为 400, N iSi

600

?之间的变化是比较稳定的。 但是, 随着温度上C

到 700, 800 ?时, 对于小于 20 厚的升 C nm N i 薄膜来 说, 其方块电阻迅速增大, 即出现了由N 向相的转变。对于厚度大于 30 的iSi N iSi2 nm N 薄膜来说, 其 方块电阻在这个温度范围变化不i

大; 直到 800 ?以 上时, 才出现了由向C N iSi N

相的转变。并且, 随iSi2

[ 21 ]尖峰所引起的漏电着线宽的减小, 无论是小于 20 的薄膜, 还。研究发现, 即使采用相 Co Six nm N i

是 大于 30 的薄膜, 向相的转变同的工艺, 不同批次 的二极管, 其漏电也有很 nm N i N iSi N iSi2 Co Si2 温度 都下降到 650, 700 ?之间。 目前还没有明大的不同。 因此, 在研究漏电的过程中, 统计分析尤 C

确充分 的理论来解释这种现象。 其重要。 实验发现, 漏电与结的周长没有很大的关

系, 而与结的面积有很大的关系。 这说明, 漏电流是 314 不同硅化物形成的浅结的漏电机理分析与

300 的结 在结的面上产生的。研究发现, 半径为 Λm 改善

() 有很大的漏电 与没有硅化物的结相比; 当半径减 对 薄膜形成的浅结进行的漏电分析发 T iSi2 [ 18 ] + 小到 100 时, 大约有 50% 的结的漏电减小到没 Λm 现, 对于 浅结, 硅化物形成前后的二极管的 p n + 有硅化物的结的水平; 当半径减小到 50 时, 大 Λm 反向 2特性基本是一样的; 而对于 浅结, 硅 I V np

约有 80% 的结漏电减小到没有硅化物的结的水平。 化物形成前后的二极管的反向 2特性有明显的 I V

这个结果表明, 漏电流并不是均匀地流过整个结面 不同, 硅化物形成后的二极管漏电要比未形成硅化

积, 而是通过很多固定的点, 而这些点是随机的分布 物时的漏电大两个数量级。这表明, 在硅化物形成的

在结的附近。基于上面的结论, 可以设想如下的漏电 过程中, 在结附近产生了大量的陷阱中心。 然而, 由

模式: 引起漏电流的缺陷点随机分布在衬底上, 在此 于反向漏电随着所加的电压呈指数增长的规律, 因

衬底上制备大、中、小面积的结。可以明显地看出, 大 此, 根据 2曲线, 很难判断出漏电产生的机理。进 I V

面积的结上有较多的缺陷点, 大约有 25% 的中面积 一步的研究发现, 在低温区域 (300 ) 附近, 无论硅 K

结上没有缺陷点, 而小面积结占到了 88%。 研究发 化物是否形成, 所有二极管的激活能都小于 2 ?E g

现, 不同的 工艺引起漏电流强烈的变化。 在 R TA (为硅的禁带宽度)。由于产生漏电流的杂质的激 E g

温度由 400 ?升高到 950 ?的过程中, 漏电 R TA C C (在扩散机制中) , 或接 活能在理论上应该接近于 g E

流的变化为: 在 400, 450 ?的过程中, 漏电流不断 C 近于 2 (在复合机制中)。因此, 在低温区域, 漏电 ?E g

增加, 在 450 ?时达到最大值; 随后, 漏电流逐渐减 C 流是由于产生或复合以及其它造成电场增强的工艺

小, 在温度为 850 ?时达到最小; 温度再升高, 漏电 C 所引起的。而在高温区域 (500 ) 附近, 硅化物形成 K

流开始增加。 分析发现, 在 400, 450 ?过程T EM C 前的激活能接近于 (对于面二极管尤其明显) , 而E g + 中, 位于硅化物和衬底硅界面处的 尖峰逐渐 硅化物形成后的激活能明显小于 (对于 浅Co Six E g np + 结)。 激活能的减小证明了硅化物过程在 浅结 , 在 450 ?时达到最大值 (20, 100 )。 这么 长大np C nm 处产生了大量额外的浅能级。而对于线形二极管, 在 长的尖峰足以穿透浅结, 而引起最大的漏电 流。 所有的温度范围, 无论是否硅化, 激活能都小于 。 表明, 在 450 ?时, 这些尖峰为 。以后, 随 E gXRD C Co 2S i这主要是由于位于表面边界处的陷阱在线形二极管 着温度的升高, 尖峰渐渐变小, 在 800 ?时完全消 C + 中的作用更加明显。研究发现, 对于 浅结, 硅化 失, 硅化物和衬底硅界面非常光滑。这与漏电流的变 p n

物形成前后的二极管化规律是相符的。 而在 , 其正向 2特性基本是一样 900 ?以上时, 漏电流的增 I V C

加主要是由于在如此高温下, 薄膜开始熔化, 的, 对于面二极管和线形二极管, 理想因子分别为 Co Si2 1104 和 1141。这表明, 正向电流主要为扩散电流, 并 使 原子偶然扩散到 衬底中所引起的。 Co Si S IM S

曲线也证明了这一点。并且, 此时的漏电流不再依赖 且在硅化物形成后有一部分的复合电流。 而对于 + 于结的面积。 因此, 在低于 850 ?时的漏电流是由 浅结, 硅化物形成前后的二极管的正向 2特 C np I V

于 尖峰所引起的, 而在 900 ?以上的漏电流 Co Six C 性有明显的不同, 在没有硅化物的二极管中, 对于面

则是由于 原子的扩散而引起的。 人们把第二次 Co 二极管和线形二极管, 理想因子分别为 1106 和

+ 温度优化设在 800 ?和 850 ?之间。R TA C C 1137, 与 结相近。然而, 对于形成硅化物的二极 p n

对于薄膜所形成浅结的漏电, 主要有两N iSi 管, 其面二极管和线形二极管的理想因子几乎是一

种 原因: 1) 在 700 ?或 700 ?以上的热退火工艺C C 样的, 为 1107。 这表明, 正向电流主要为扩散电流, [ 22 ]在浅 ) 结处形成了肖特基接触; 2在硅化物的形并且要比没有形成硅化物的大 3 个数量级。 研究发 [ 23 ]成过程 中, 硅化物和衬底的界面氧化。 现, 这主要是由于金属 或 穿透结并和衬底 T i T iSi2

在 2(222) 浅 N iSa licide N iselfa lignedsilicidat io n 形成肖特基接触而引起的。 + 结中, 性能较好的二极管的正向电流主要是由 或 P对于 薄膜所形成浅结的漏电, 有很多原 Co Si2 + [ 19, 20 ] 区的载流子扩散所引起的; 而性能较差的二极管N 因, 其 中 最 常 见 的 为 在 硅 化 物 形 成 过 程 中

[ 3 ] , , 21 的正向电流和反向电流则主要是由于 薄膜偶 Schw ade U N epp l FT acob s E P T aSi2 gate fo r N iSi + + [] 1 , VL S I CM O S circu its J IEEE T ran s E lec D ev然地渗透 或区, 而到达 或 区, 形成肖特 PN N P () 1984, 31 7: 98829921 基接触而引起的。研究还发现, 饱和电流并不是复合 [ 4 ] 2221 2, , , T saiM YChao H H Eph rath L M et alO nem i2 (电流, 这是因为, 一方面, 尽管理想因子明显高 1112 2() cron po lycide W Si2 on po lysiM O SFET techno logy ) , 1113, 但却远远小于 2; 另一方面, 在正向电压增 []1 222141, 1981, 128 (10): 2207J J E lectrochem Soc 加到串联电阻效应非常明显时, 理想因子仍然保持 [ 5 ] , , , 1 Fukumo to M Sh inohara A O kada Set alA new

?2常数。而对于有明显复合电流的二极管来说, 其正向 M o Si2 th in po lyS i gate p rocess techno logy w ithou t

[]1 dielectric degradat io n of a gate ox ide J IEEE T ran s 2曲线有两个明显的理想因子, 在低压区的值大 I V , 1984, 31 (10): 1432214391E lec D ev 于 1, 而在高压区的值接近于 1。由此可以看出, 性能 [ 6 ] 2221 , , , M u rarka SP F raster D B Sinha A Ket alR efrac2 较差的二极管, 在正向偏压下, 复合电流不是主要电 2to ry silicides of t itan ium and tan talum fo r low resistiv2 流。 对于性能较差的二极管, 在 015 的反向电压 V 1 [] ity gates and in terconnects J IEEE T ran s E lec 下, 其饱和电流和反向电流的活化能为 0162, 0158 , 1980, 27 (8) : 1409214171D ev

[ 7 ] 2, 2, 2, 1 W ang KL Ho llow ay T C P in izzo t to R F et al, 理想势垒高度为 0167, 0164 , 远小于 的 eV eV Si + 22?Compo site T iSi2 npo lyS i low resistivity gate elec2 能带宽度 (1112 ) , 但非常接近 2的势垒 ?eV N iSinS i t rode and in terconnect fo r VL S I device techno logy 高度 (0165 )。这也证明了肖特基接触是二极管性 eV []1 , 1982, 17 (2) : 17721831J IEEE J So l Sta C irc 能变坏的主要原因。 实际上, 在高反向电压下, 二极 [ 8 ] 2, 21 22N g KKL ynch W T A nalysis of the gatevo ltage 管的反向电流主要是由隧道电流引起的。 这是因为 ’1 []dependen t series resistance on M O SFET s J IEEE 2 12 ?, 1986, 33 (7) : 96529721与 曲线的陡度远大于理论值, 温度对反向 T ran s E lec D ev ?IR T E

[ 9 ] 221 , N g KKL ynch W T T he im pact of in t rin sic series 2特性的影响也进一步证明了上述结论。I V []1 resistance on M O SFET scaling J IEEE T ran s E lec 可以通过以下方法来减小漏电流: 利用 覆 T iN , 1987, 34 (3) : 50325111D ev [ 22 ][ 24 ][ 23 ] 盖、掺杂、覆盖, 所有这些方法都是用 N T i[ 10 ] , , , 1 O hgu ro T N akam u ra Sko ike M et alA nalysis of 覆盖层或掺入的杂质来抑制表面氧化, 并抑制表面 2 2resistance behav io r T iand N isalicided po lysilicon 的粗糙, 以减小漏电流。 [] 1 , 1994, 42 ( 12 ) : film s J IEEE T ran s E lec D ev

2305223171

[ 11 ] 2221 , , , L asky J B N ako s J SCain O J et alComparison 4 结 论 2of t ran sfo rm at io n to low resistivity phase and agglom 2 []1 , erat io n of T iSi2 and Co Si2 J IEEE T ran s E lec D ev讨论了适用于深亚微米 器件的几种自 CM O S () 1991, 38 2: 26222591

对准硅化物 (、、工艺, 并对不同的硅化物工 ) T iCoN i[ 12 ] 221 , M endicino M A Seebauer E GK inetics of salicide

21 []艺及硅化物薄膜性能进行了对比和分析。结果表明, con tact fo rm at io n fo r th inf ilm SO I t ran sisto rs J J

, 1995, 1429 (2) : 282301E lectrochem SocL L 随着器件特征尺寸的缩减, 常规 和 的自对准 T i Co [ 13 ] , , , 1 2 M o r im o to T O hgu ro T M omoo se Set alSelf硅化物已经不能满足器件性能的要求。的自对准 N i 222aligned n ickelm ono silicide techno logy fo r h ighspeed 硅化物由于具有一系列的优点而成为 和 的 T i Co [] 1 deep subm icrom eter logic CM O S UL S I J IEEE 自对准硅化物有力的竞争者。的自对准硅化物不N i , 1995, 42 (2) : 91529221T ran s E lec D ev

[ 14 ] 2, 2, 2, 1 Xu D X D as SR Peters C J et alM aterial aspects

[]1 of n ickel silicide fo r UL S I app licat io n s J T h in So lid

, 1998, 326 (122) : 14321501F ilm 但可以满足器件进一步缩小到超深亚微米的需要, [ 15] , 21 , , Chen J Co linge J P F landre D et alComparison of 而且可以满足器件进一步缩减到纳米范围的需要。 , 2222T iSi2 Co Si2 and N iSi fo r th inf ilm silicono nin su la to r

[] 1 , 1997, 144 (7 ):app licat io n s J J E lectrochem Soc

参 考 文 献: 243722442, 221 [ 16 ] , , , SPey KL M angelinck D et alIm p roved L ee P

[ 1 ] 2, 2, 2, 1 Sara sw at KC Boo rs P L Fair J A et alP roperties ?2??N iSi SAL IC ID E p rocess u sing p resilicide nsub + 2of low p ressu re CVD tungsten silicide fo r M O S VL S I ?[] 1 supim p lan t fo r M O SFET s J IEEE T ran s E lec

[]1 , 1983, 30in terconnect io n J IEEE T ran s E lec D ev , 2000, 21 (12): 56625681D ev L ett

()[ 17 ] 221 , , , 11: 1497214511 L ee P SPey KL M angelinck D et alN ew salici2

( ) dat io n techno logy w ith N i P t alloy fo r M O SFET s [ 2 ] , , , 1 M och izuk i T T su jim ara T Kash iw agiM et alF ilm p

[]1 , 2001, 22 (12): 5682 J IEEE T ran s E lec D ev L ett2 roperties of M o Si2 and their app licat io n to selfaligned 5701 [] 1 , M o Si2 gate M O SFET J IEEE T ran s E lec D ev()下转第 639 页 1980, 27 (8) : 1431214351

抗 性能要比 5片和 片好。4片在 2 000 能力要比体硅差, 但是, 我们通过采用栅 路抗 ESD H H S V ESD

应力之后所有管脚都完好, 而 5片在 1 500 应力 H V 控二极管结构和适当的限流电阻组成的保护电路, 之后就有管脚失效。 另外, 23 片和 21 片同样在 SH 也能够获得可以让人接受的抗 性能, 而且并不 ESD 1 500 下, 23 片的失效管脚数要比 21 片少得 V SH 需要增加额外的工艺步骤和掩膜版。 多。 参 考 文 献: 313 讨论

为了解决实验中出现的限流电阻被烧毁的问 [ 1 ] 考林基 1 技术—— 21 世纪的硅集成电路技术J P SO I + 题, 我们在工艺上做了些改进, 在 电阻上面做了 P[]1 北京: 科学出版社, 19931M 硅化物, 使其电阻值变小, 片和 片是没有做硅 S H [ 2 ] , , , 1 Chan M SYuen S SM a Z J et alESD reliab ility 化物, 而 4片和 5片是做过硅化物的。21 片在 S H H and p ro tect io n schem es in SO I CM O S ou tpu t buffers

1 500 应力之后所有的输入端都被打坏了, 原因 V [ ] 1 2 , 1995, 42 ( 10 ) : 1816J IEEE T ran s E lec D ev就是限流电阻被烧毁; 而 521325 片在 1500 应力 H V 18201 之后输入端都是好的。 片和 5片的情况也一样, S S [ 3 ] 张兴, 石涌泉, 黄敞 1 高速 ?电路输入保护CM O SSO I 23 片在 1 500 应力之后, 部分输入端的限流电阻 SV 网络的优化设计[] 1 微电子学与计算机, 1993, 10J 被打断了; 而 429 片在 2 000 应力之后, 输入端 SV () 1: 412441 都是好的。另外, 从实验结果上, 我们发现硅膜越厚, [ 4 ] , , , 1 V o ldm an SA ssaderagh i FM ande lm an J et al电路抗 能力就越强。但是, 由于 本身特性 ESD SO I 22[]1 CM O So nSO I ESD p ro tect io n netw o rk sJ J E lec2 的要求, 硅膜厚度会影响到 其它方面的特性, SO I 23501, 1998, 42 (4) : 333t ro statics 需要折中考虑。 所以, 这个并不能作为提高电路抗 [ 5 ] 王颖 1 集成电路 保护技术研究[]1 微电子M O S ESD J 能力的途径。ESD () 技术, 2002, 30 1: 242281 由于用的材料是 电源和地之间没有寄生 , SO I 的二极管, 因此, 使电源和地之间的抗 能力比 ESD () 作者简介: 汤仙明 1979- , 江苏溧阳人, 较弱, 影响了整个电路的抗 能力。ESD 硕士研究生, 主要研究方向为 保 SO I ESD 护电路。

4 结 论

虽然由于 本身的材料结构原因, 使 电SO I SO I

()上接第 635 页 2 of eno rm ou sly large junct io n leakage cu rren t in n ickel

2[ 18 ] 21 silicided ntype diffu sed layers and its im p rovem ent L ee H D Characteriazt io n of shallow silicided junc2 []1 []1 1993 11921A Ex t A b str SSDM C 2 t io n fo r subqua rter m icron UL S I techno logy ex t rac2 [ 23] 2, 2, 21 []1Hou T H L ei T F Chao T SIm p rovem en t of junc2 t io n of silicidat io n induced scho t tky con tact area J

2t io n leakage of n ickel silicided junct io n by a T icapp ing 27671, 2000, 47 (2) : 762IEEE T ran s E lec D ev

1 [], 1999, 20 (11):layer J IEEE T ran s E lec D ev L ett [ 19 ] 2221 , , , Kang W T K im J SL ee KYet alT he leakage

57225731 cu rren t im p rovem en t in an u lt rashallow junct io n

[ 24] , , , 1 2O hgu ro T N akam u ra SM o rifu ji Eet alN it rogen [] 1 NM O S w ith Co silicided sou rce and drain J IEEE

2 doped n ickel mono silicide techn ique fo r deep subm i2111, 2000, 21 (1) : 9T ran s E lec D ev L ett

1 1 19951 45324561[][]cron CM O S salicide A IEDM C [ 20 ] 2221 , , , Cho i C J Seong T YL ee KM et alA bno rm al + ?: junct io n p rofile of silicided pn shallow junct io n sa () () 作者简介: 王大海 1976- , 男 汉族, 河 [] 1 , leakage m echan ism J IEEE T ran s E lec D ev L ett

() 南省南阳人, 硕士研究生, 1999 年毕业于 2002, 23 4: 18821901

[ 21 ] 21 , , , Go to KIFu sh ida A W atanabe J et alA new leak2 长春理工大学, 获工学学士学位, 主要从事

age m echan ism of Co salicide and op t im ized p rocess 深亚微米 技术和纳米器件的 CM O S VL S I [] 1 , 1999, 46 ( 1): condit io n J IEEE T ran s E lec D ev研究。 11721241

[ 22 ] , , , 1 O hgu ro T M o romo to T U sh iku Yet alA nalysis

范文二:自对准双栅MOSFET的结构与工艺实现_钱莉

Structures and Processes of Self -Aligned Double -Gate MOSFETs

QIA N Li , LI W eihua

(Micro electronics center , So utheast U ni vers ity , Nanjing , 210096P . R . China )

A bstract : Double -gate MOSFE T is considered the most promising candidate for sub 50nm MOSFET design , which of -fers superior subthreshold slope , better shortchannel control , and higher mobility . Self -aligned double -gate device struc -ture is proposed to accommodate the key features of the ideal double -gate MOSFE T . In this paper , we present several kinds of self -aligned double -gate MOSFET structur es and their pr ocess flows . Key words : Self -Aligned gates ; Double -Gate MOSFETs EEACC : 2570D 2570F

自对准双栅 MOSFET 的结构与工艺实现

①

钱 莉 , 李伟华

(东南大 学微电子中心 MEMS 教育部重点实验室 , 南京 210096)

摘要 :双栅 MOSFET 是一 种非常有发展前途的新型器件 , 它具有跨导高 、 亚阈值特性优异 、 短沟道特性好等优点 。 自 对准的双栅 MOSFET 结构中 , 栅与源漏之间无覆盖 , 对于实现最终的高性能十 分重要 。 本文具体介绍了几种自对准 的双栅 MOSFET 的结构及其工艺流程 。 关键词 :自对准栅 ; 双栅 MOSFET

中图分类号 :TN4 文献标识码 :A 文章 编号 :1005-9490(2002) 03-0287-05

1 引 言

CMOS 器件的尺寸的不断缩小 , 大大提高了集成 密度 , 改善了电路性能 。 但是 , 当栅长缩小到几十纳 米量级 时 , 由于 二级 效应 的影 响 , 如 短沟 道效 应 、 DIBL 等 , 常规结构的 C MOS 器件已经达到了物理极 限 [1]

。 因此需要研究新型的器件结构以克服和改善 这些寄生效应的影响 。 双栅 MOSFE T 是一种比较有 前途的新型器件

。

图 1 基本的双栅 MOSFET 结构示意图

由于双栅 MOSFE T (如图 1) 具有上 、 下两个 栅 ,

增强了对沟道的控制能力 。 如果硅膜较薄 , 将会出 现体反型 , 整个硅膜处于强反型状态 , 硅膜中电势基 本相等 。 在这 种状况下 , 导电 沟道处于 体内 , 双栅 MOSFE T 器件的载流子迁移率 、 漏源电流 、 亚阈值特

性都会有很大提高 [2]

。

双栅 MOSFET 结构中 , 上 、 下栅的对准是个十分 重要的问题

[3]

。 如果上 、 下栅不能对准 , 则会增加栅

与源漏之间的覆盖电容 , 减小电流驱动能力 , 影响器

件的频率特性 。 因此只有上 、 下栅自对准的结构 , 才 能最终实现双栅 MOSFE T 的高性能 。

近几年来 , 在基本的双栅 MOSFE T 结构的基础

上发展了许多新型的自对准结构 。 下面具体介绍几 种自对准的双栅 MOSFE T 的结构及其工艺流程 。

第 25卷第 3期 2002年 9月 电 子 器 件 Chinese Journal of Electr on Devices

Vol . 25, No . 3

Sep . , 2002

-04-

2 自对准的双栅 MOSFET 的结构

2. 1 通过沟道横向选择外延制备源漏区的自对准 双栅 MOSFE T [4]

这种结构的制备 , 首先通过硅片键合及背面减 薄技术 , 得到单晶的沟道区和上 、 下栅极 。 再一步刻 蚀出上 、 下栅及沟道区 , 然后采用横向选择外延 , 形 成器件的源漏区 , 最终结构如图 2(e ) 。

大致的工艺流程为 (如图 2) :

(1) 在 SOI 衬底上生长一层薄的氧化层作为 下栅氧化层 , 然后在其上淀积多晶硅作为下栅极 , 随 后再在多晶硅上淀积一层 低温热氧化层 (LTO ) , 并 对其进行化学机械抛光 (C MP ) , 用于下一步键合使 用 (如图 2(a ) ) 。

(2) 将上一步做好的整个硅片倒置过来 , 使抛 光的 LTO 层与另一作支撑的硅片键合 , 并背面减薄 , 以埋氧化层为停止层腐蚀掉背面硅片 。 再将硅膜上 的埋层氧化层腐蚀掉 , 使得薄的硅膜暴露出来 。 然 后在硅膜上生长一层薄氧化层作为上栅氧化层 , 在 薄氧化层上淀积多晶硅作为上栅极 (如图 2(b ) ) 。 (3) 淀积一层隔离氧化层和一层隔离氮化物 , 将上 、 下栅一起刻蚀 , 以抛光的 LTO 为停止层 , 这样 上 、 下栅肯定是自对准的 (如图 2(c ) ) 。

(4) 利用高掺杂浓度的上 、 下多晶栅与轻掺杂 浓度的沟道区之间的氧化速率的差异 , 在多晶硅的 边墙上生长一层较厚的隔离氧化层 , 而沟道两侧只 生长较薄的氧化层 (如图 2(d ) ) 。

(5) 刻蚀掉沟道两侧的薄氧化层后 , 在暴露的 沟道两侧进行选择性外延 。 这样 , 在沟道的两侧形 成单晶的源漏 (如图 2(e ) ) 。 由于外延硅的生长受到 表面处二氧化硅的抑制 , 所以外延形成的源漏区呈 现特定的形状 。

(6) 后序工艺制作 。

2. 2 垂直沟道的自对准双栅 MOSFET [5]

这种结构中 , 双栅 MOSFET 的沟道垂直于硅衬 底 , 栅分别在两侧 , 而源漏区分别在上面和下面 。 它 是首先在衬底上掺杂外延形成源区 , 再形成沟道区 和上面的漏区 , 再一步制作两个棚极 。 单晶沟道区 是通过衬底选择外延来实现的 , 最终结构如图 3(f ) 。 大致的工艺流程为 (如图 3) :

(1) 在硅衬底上外延一层 n +层作为源 极 , 并

图 2 横向选择外 延制备源漏区的

自对准双栅 MOSFE T 的工艺流程

层 , 将磷硅玻璃 (PSG ) 、 氮化物 、 二氧化硅 、 氮化物 、 磷 硅玻璃 、 氮化物依次淀积在很薄的二氧化硅层上 (如 图 3(a ) ) 。

+,

288

电 子 器 件 第 25卷

图 3 垂直沟道的自对准双栅 MOSFET 的工 艺流程 个 垂直 的穿通所有物质的窗口 。 在窗口处 , 从源极开始 进 ,

(3) 以 最 上 层 的 氮化 物 层 为 基 准面 , 进 行 CMP , 去 掉多余的 外延 硅 , 淀 积多晶 硅 , 形成 n +漏 极 , 再在其上淀积一层氮化物 (如图 3(c ) ) 。

(4) 以中间的厚氧化层为停止面 , 将漏极和上 层 PSG 一同刻蚀出图形 。 接着在其上淀积氮化物作 为隔离层 , 并刻蚀出图形 。 这时上层剩下的磷硅玻 璃已被包在氮化物隔离层中 (如图 3(d ) ) 。

(5) 以氮化物隔离层和下层 PSG 上的氮化物 为停止面 , 将中间的厚氧化层腐蚀掉 , 使得沟道暴露 出来 (如图 3(e ) ) 。

(6) 在暴露的沟道侧面生长一层薄的二氧化 硅作为栅氧化层 , 淀积多晶硅栅 , 并刻蚀出图形 (如 图 3(f ) ) , 这样器件的两个栅肯定能实现自对准 。 作 为牺牲层的中间厚氧化层厚度直接决定了器件的栅 长 (L g ) 。

(7) 后序工艺制作 。

2. 3 FinFET 结构 [6, 7]

FinFE T 属于 窄 沟道 形式 (如图 6(d ) ) 的 双 栅 MOSFE T , 它是先制作窄的沟道区 , 再在 沟道区的两 边形成源漏区 , 然后再一步制作两个栅极 , 最终结构 如图 4(f ) 。

大致的工艺流程为 (如图 4) :

(1) 先利用热氧化的方法将埋层氧化层上 SOI 膜减薄至所需的厚度 , 采用离子注入法将减薄后的 硅膜掺杂 , 接着在硅膜上生长一层薄氧化层 (如图 4 (a ) ) 。

(2) 光刻出图形 , 形成狭窄的硅脊 (即导电沟 道 ) (如图 4(b ) ) 。

(3) 在硅脊上先后淀积一层硼掺杂 SiGe 和一 层较厚的 LTO (如图 4(c ) ) 。 采用硼掺杂的 SiGe 而 不用硼掺杂的 Si 来制备源漏区 , 是因为 P 型 SiGe 的 电阻系数 远远小 于相同 掺杂 浓度的 P 型 Si , 而 且 SiGe 还提供与硅脊两侧的表面良好的电接触 。 (4) 将 LTO 和 SiGe 有膜刻蚀出图形 , 从而形 成源漏区 (如图 4(d ) ) 。

(5) 在源漏分隔区的侧面边墙上 LPC VD 一层 氮化物 , 刻蚀出图形 , 使得仅露出中间的沟道区 (如 图 4(e ) ) 。

(6) 在氮化物隔离层之间的硅脊侧面上 , 高温 生长一层薄的氧化层 。 在这个高温氧化步骤以及后 面的退火步骤的共同作用下 , 凸起的源漏区下的硼 离子被驱赶到氮化物隔离层下的硅脊内 , 从而形成 +

289

第 3期 钱 莉 , 李伟华 :自对准双栅 MOSFET 的结构与 工艺实现

图 4 FinFE T 结构的工艺流程 4(f ) ) 。

2. 4 通过凸槽来实现自对准的双栅 MOSFE T [8]这种结构中 , 先形成下栅极 , 再淀积一层无定形 α-Si , 并在硅膜上留下一个和下栅极相对齐的凹槽 , 通过这个凹槽来实现上 、 下栅的自对准 。 然后采用 金属诱导横向结晶 (MILC ) 技术 , 使无定形 α-Si 单晶 化 , 形成单晶的沟道区 , 最终结构如图 5(d ) ) 。 大致的工艺流程为 (如图 5) :

图 5 通过凹槽来实现自对准的

双栅 MOSFE T 工艺流程

(1) 在硅衬底上 , 生长一层厚的 LTO 层 , 在上 面淀积多晶作为下栅极 , 并刻蚀出图形 , 生长一层薄 氧化层 , 作为下栅极的栅氧 , 再在上面再淀积一层氮 化物 , 再淀积一层无定形 α-Si , C MP 无定形 α-Si , 直到 露出氮化物层 (如图 5(a ) ) 。

(2) 用热 H 3PO 4去除掉 SiO 2上的氮化物 , 直 到露出氧化层 (如图 5(b ) ) 。

(3) LPCVD 一层无定形硅 α-Si 。 因为上 一步 的操作 , 使得在源漏处形成台阶 , 这样再淀积一层无 ,

290

电 子 器 件 第 25卷

源漏区 , 并形成一个凹槽 , 保证淀积上栅极时 , 可以 和下栅极自动对准 (如图 5(c ) ) 。

(4) 采用金属诱导横向结晶 (MILC ) 技术 , 使无 定形 α-Si 膜重结晶为单晶硅膜 , 作为器件的源漏区 和沟道区 。 刻蚀出器件的有源区 , 生长积一层薄氧 化层作为上栅氧 , 再淀积多晶作为上栅极 , C MP 多晶 层使得正好与凹槽相平 。 这样上 、 下栅就能实现自 对准 (如图 5(d ) ) 。

(5) 后序工艺制作 。

3 总 结

双栅 MOSFET 比普通体硅 MOSFET 性能 优越 , 它具有跨导高 、 亚阈值特性优异 、 短沟道特性好等优 点 。 上 、 下栅自对准 的双栅 MOSFE T 才能最终实现 双 栅 MOSFE T 的优 异的性 能 。 因 此自对 准的双 栅 MOSFE T 的结构设计与工艺研究具有十分重要的意 义 。

参 考 文 献

[1] H . -S . Philip Wong , Beyond the Conventional MOSFET ,

E SSDERC 2001.

[2] 沈寅华 , 李伟 华 。 双栅 MOSFET 的研 究和发 展 [J ]。 微

电子学 , 2001年第 30卷第 5期 , 290~293

[3] Hon -Sum Philip Wong , Kevin K , Chan , et al . Self -Aligned

(Top and Bottom ) Double -Gate MOSFET with a 25n m Thick

Silicon Channel [J ]. IEDM Tech Dig , 1997; 427~430[4] Jong -Ho Lee , Youn g -June Park , et al . Super Self -Aligned

Double -Gate (SSDG ) MOSFE Ts Utilizing Oxidation Rate Dif -ference and Selective Epitaxy [J ]. IEDM Tech Dig , 1999; 71~74

[5] Hergenrother J M , Monroe D , et al . The Vertical Replace -ment -Gate (VR G ) MOSFET :A 50-nm Vertical MOSFET with Lithography -Independent Gate Length [J ]. IEDM Tech . Dig , 1999; 75~78

[6] Xuejue Huang , Wen -Chin Lee , et al . Sub 50-nm FinFET :

PMOS [J ]. IE DM Tech Dig , 1999; 67~70

[7] Xuejue Huang , Wen -Chin Lee , et al . Sub -50nm P -Channel

FinFET [J ]. IEEE Transactions on Electron Devices , 2001; 48[5]:880~886

[8] Shengdong Zhang , Mansun Chan , et al . Fabrication and

properties of self -aligned double -gate poly -Si TFT [J ]. Solid -State and Integrated -Circuit Technology , 2001; 1442~1445[9] Erin C . Jones , Meikei Ieong , et al . High Performance of

Planar Double Gate MOSFE Ts with Backgate Dielectrics [C ]. In :Device Research Conference , 2001; 28~29

[10] Moers J , Trellenkamp S , et al . Vertical Double -Gate MOS -FE T based on epitaxial growth by LPCVD . ESSDERC 2001[11] Taichi Su , John P Denton et al . New Planar Self -Aligned

Double -Gate Fully -Depleted P -MOSFE T ′ s Using Epitaxial Lateral Overgrowth (ELO ) and Selectively Grown Source Drain [C ]. In :2000IEEE International SOI Conference , 110~111

[12] Xinnan Lin , Chugang Feng , et al . Double -Gate SOI MOS -FE T Fabrication from Bulk Silicon Wafer [C ]. In :2001IEEE International SOI Conference , 93~94

作者简介

钱 莉 (1978-01) 女 , 2000年获东南大学工学学士学位 , 现于东南大学电子工程系攻读硕士学位 , 主要研究 方向为新型 SOI 器件 。

291

第 3期 钱 莉 , 李伟华 :自对准双栅 MOSFET 的结构与 工艺实现

范文三:【doc】亚微米自对准硅化物工艺开发

亚微米自对准硅化物工艺开发

第6卷.第3划

Vol6.

NO3

电子与封装

ELECTR0NICS&PACKAGING

总第35期

2006年3月

,

微,电子:制遣一,与可一靠牲

亚微米自对准硅化物工艺开发

刘允,陈海峰

(中国电子科技集团公司第58研究所,江苏无锡214035)

摘要:文章对亚微米自对准硅化物制造设备及工艺进行了详细的描述.文中以实际生产为目标,

以实验数据为依据,对影响自对准硅化物薄膜特性的各~i-y--:E参数进行调试和论证,找出合适的RTP1

温度,并开发出适合自对准硅化物薄膜的工艺标准.

关键词:自对准硅化物;硅化物桥;电阻率;转移曲线;RTP退火

中图分类号:TN305文献标识码:A文章编

号:1681-1070(2006)03-37?03

TheDevelopmentofSalicideinSub-micronProcess

LiuYun,ChenHai-feng

(ChinaElectronicsTechnologyGroupCorporationNo.58ResearchInstitute,WuxiJiangsu214035,China

Abstract:Thisarticledescribestheprocessandequipmentofsalicideinsub-micronprocess.

Forthepurpose

ofproduction,

basedonexperimentdata,thisexperimentexaminesseveralprocessparametersthateffect

thesalicidefilmpropertiestofindouttheproperRTP1temperature,

anddevelopcorrespondingsalicide

processrules.

Keywords:Salicide;SilicideBridge;Resistivity;TransformationCurve;RTPAnneal

1自对准硅化物工艺介绍

当器件特征尺寸进一步缩小至1m以下时,提

出了降低同器件相串联的扩散区薄层电阻和接触电阻

的需要,导致在80年代初期产生了自对准硅化物

(self-alignedsilicide)T艺.该工艺在源,漏和栅

均有硅化物形成,它利用多晶硅侧壁氧化物,通过

金属与裸硅区域的反应达到自对准.同Polyside工艺

中的硅化物相比,自对准硅化物工艺的硅化物除

BPSG回流外不经高温退火,故高温稳定性要求不

高.实际E,自对准硅化物T艺中的金属必须在一

定温度下同硅反应.

自对准硅化物T艺通过在源漏覆盖高电导率的硅

收稿日期:2005-10-05

化物降低了扩散电阻,通过增加有效接触面积降低了

接触电阻.

本文中采用钛与硅反应获得TiSi:,当形成稳定

的C54相位时,它具有较高的电导率,因此虽然其

热稳定性一般,仍是自对准硅化物工艺的首选.

自对准硅化物工艺为了实现自对准总共需要两大

工艺过程:

(1)Ti淀积.

(2)TiSi,硅化物形成过程:

?RTP1工艺形成C49相位的TiSi2;

?选择性腐蚀工艺除去未反应的Ti和顶层的TiN

膜;

?RTP2形成稳定的C54相位低电阻率TiSi:薄膜.

.

37.

第6卷第3期电子与封装

Ti淀移{

形成TiSi2

图1自对准硅化物工艺过程

为什么我们需要两步RTP和一次选择性腐蚀来完

成稳定的C54相位低电阻率TiSi薄膜呢?南于在Ti-si

的反应中,si作为主要的扩散剂,若温度太高,衬

底的Si就有可能扩散到隔离层上的Ti中,这样就会

形成栅极和源漏间的短路,即我们常说的硅化物桥现

象,因此采用第一次RTP用低温方式形成C49相位的

TiSi,利用选择性腐蚀工艺除去未反应的Ti和顶层的

TiN膜,腐蚀液对TiSi与Ti和顶层的TiN选择比很

高,C49和C54相位的TiSi,腐蚀量很少,腐蚀工艺

之后只有在栅极和源漏极留有TiSi,,其他地方都被漂

光,这就是自对准工艺.最后用高温RTP将TiSi由

C49相位转换成C54相位低电阻率TiSi薄膜,这样在

RTP的高温工艺过程中,隔离层上就没有Ti,这也

就不会有硅化物桥现象.

这其中RTP1的温度选择是关键,对于各种Ti淀

积膜厚,各种RTP设备的设定点都不同,温度若过

高,有可能会有硅化物桥现象,温度过低则TiSi,薄

膜偏薄,接触电阻过大,无法满足丁艺要求.

离层

Ti

离层

TiSi2

图2硅化物桥现象

本文着重讨论在55nm的Ti淀积厚度下,作出RTP

的转移曲线并选择合适的RTP1的温度.

.

38.

2自对准硅化物工艺模块开发过程

2.

1PVD淀积Ti

设备采用美国应用材料公司的EnduraPVD.按

照工艺要求采用55nm厚度Ti,工艺菜单如表1所示.

表1Ti淀积工艺参数

工艺参数参数设置

真空本底

溅射工艺压力

溅射[艺气体

溅射工艺功率

溅射工艺时间

基座温度

<133.3224×10—Pa

799.9344Pa

氩气

加热气体

淀积功率:2000W

淀积时间:31s

O?

由于在Ti-Si的反应中,Si作为主要的扩散剂,

所以Ti采用常温淀积(加热器设为0oC,这样形成

的多孔状结构在RTP工艺时有利于Si的扩散,容易形

成TiSi,.同时淀积功率不能太高,这样有利于膜厚

的控制.

2.

2TiSi,硅化物形成过程

2.

2.1工艺准备

RTP设备采用韩国制造的KORONARTP600A,

采用红外高温计并利用PID方法来精确控制高温.

图3红外高温计控温模块图

RTP的高温阶段采用高温计来检测硅片背部的辐

射系数来控温(图3),影响辐射系数的主要参数

有:

?硅片背面的薄膜材料;

?硅片背面的平整度;

?T艺温度<700~{2时硅片正面若是透明薄膜也会

第6卷第3期刘允,陈海峰:亚微米白对准硅化物T艺开发

产生影响.

众所周知硅片背面的多晶硅薄膜和二氧化硅薄膜

对温度控制有很大的影响,实际温度由于薄膜厚度和

材料的不同会高于或低于控制温度,为了更精确地控

温,T艺前需做以下准备:

?采用专用软件和裸硅片测试高温计响应来对高

温计控制模块校准;

?对硅片进行去背面处理,保证工艺温度的片间

和批问均匀性.

2.2.2TiSi,转移曲线的绘制

-一

旦确定好所淀积的Ti膜厚以及校准完高温计控

制模块,首要的工作就是作出Ti-Si反应的转移曲线,

找到合适的RTP1温度.常规的方法是在裸硅上淀积

上所需厚度的Ti,并做第一次RTP工艺(RTP1),

RTP1工艺温度从600%~850~C每25?拉一个条件,丁

艺时问都是30s.我们为了精确找到最合适的RTP1温

度,从620%~800~C,以10?为间隔,共19个点,

工艺完成后利用四探针分别测出每片的方块电阻,同

时作出方块电阻与温度之间的曲线,即转移曲线.对

于55nmTi的选择性腐蚀,我们选用常用lT艺,采用

50’E的NHOH/H2O2/H2O(1/1/5)溶液漂洗5min.

实验步骤:

?准备19片未掺杂si片;

?2%HF漂洗120s;

?PVD淀积Ti55nm;

?RTP1N,30s,温度620~C~800~,以10?为

间隔,共19个点;

?测方块电阻与片内均匀性,绘制转移曲线;

?选择性腐蚀APM(1:1:5),50,

5min;

?测方块电阻与片内均匀性,绘制转移曲线.

,-,

日

爱

鼍

芑

昌是号宾霉罢昌宝82高宝字宾88足昌宝8卜卜卜卜卜卜卜卜I”--

卜卜?

RTP1温度/?

图4RTP1后TiSi2转移曲线

55

—5O

口45

40霹盈105

O高景导景龟R曷82昌暑导宾88寓宗8

I”--I”--卜卜卜卜卜卜卜卜卜?

RTPI温度/?

3O

25

20?

-s

墨

10

5

O

图5选择性腐蚀后TiSi转移曲线

从图中可以看出RTP后的片内均匀性和方块电阻

的变化:

?RTP1后片内均匀性从720~C开始随温度升高迅

速变大,到750~E达到最大,这说明从720%C49相

位的TiSi,开始大量产生;

?而温度升高到770?时片内均匀性又降至最低且

随温度升高基本没有变化,并且选择性腐蚀后方块电

阻的变化量很小,这说明在这个温度区所淀积的Ti大

部分转化成了C54相位的TiSi,.有些公司不需要做自

对准硅化物T艺,只需做孔硅化物,则可以直接选择

这个温度区.

我们为了避免硅化物桥现象,同时降低接触电

阻,根据所绘的转移曲线,我们把RTP1工艺温度设

为740?.

对于RTP2的工艺温度设定,根据工艺资料,主

要南线宽决定,与温度设置关系不大,因此我们采

用了常规的850?.

3结束语

亚微米自对准硅化物上艺虽然在国际上已经是2O

年以前的工艺,但是对于国内的国有IC制造工艺线来

说仍然是一个全新的课题.希望通过本文能为以后开

发亚微米自对准硅化物工艺的国内工艺线提供一些正

确的思路.

作者简介:

刘允.男,1974年生,1996年

毕业于东南大学半导体物理与器件专

业,一直致力于Ic制造的生产与技术

研究.现在中国电子科技集团第58研

究所工艺生产线任职.

39.

范文四:多晶硅的应用及自对准工艺

1. 自对准技术:

自对准工艺是先在生长有栅氧化膜的硅单晶片上淀积一层多晶硅,然后在多晶硅上刻蚀出两个扩散窗口,杂质经窗口热扩散到硅单晶片内,形成源和漏扩散区,同时形成导电的多晶硅栅电极,其位置自动与源和漏的位置对准。按照这种自对准工艺,栅与源和漏的覆盖由杂质侧向扩散完成,比铝栅工艺的覆盖电容要小很多。采用离子注入掺杂工艺的杂质侧向扩散更小,用它代替硅栅工艺中的热扩散工艺,能进一步减小栅对源和漏的覆盖电容。此外,在铝栅工艺中,即使铝栅电极比沟道短,也可增加一步离子注入工艺填充栅区旁的未衔接部分,实现自对准,借以减小寄生电容,可提高MOS 集成电路的开关速度和工作频率,同时也减小器件尺寸而提高电路的集成度。

自对准工艺在隔离氧化前的工序与一般用PN 结隔离制造集成电路的工序相同。隔离氧化后,在氧化层上淀积一层厚1000~1200埃的硬Si 3N 4膜,然后套隔离区及基区的复合版,以光刻胶作为掩蔽,用等离子刻蚀方法去除隔离区及基区上的硬Si 3N 4膜,露出氧化层,用比隔离区面积稍大的掩膜版光刻隔离区,进行隔离扩散后用氢氟酸溶液漂去基区上的氧化层,到此也就完成了隔离区与基区之间的自行对准工序。随后进行基区扩散的同时进行发射区氧化,再用等离子刻蚀方法去除作为掩蔽用的硬Si 3N 4膜。自对准工艺如下页图a~f所示。

现在有一种全自对准槽栅IGBT(绝缘栅双极晶体管) 结构,其工艺简单,全套工艺只有两张光刻版,提高了工艺成品率。它独特的IGBT 沟道多重短路结构,有效地防止了器件闩锁,采用氧化层硬掩膜和硅化物工艺,实现了全自对准的多晶硅反刻和金属连接,增加了IGBT 芯片单位面积的元胞密度和沟道宽度,提高了器件的电流能力。用砷(As)掺杂代替磷(P)掺杂,有效地提高了源区表面浓度,实现了浅结工艺。整套工艺只要P +和槽栅两张掩膜版,取消了光刻套准,从而极大地缩小了IGBT 的元胞尺寸,增大了单位面积的元胞密度和沟道宽度,降低了器件的导通电阻。

2. 多晶硅在半导体工艺中的应用

多晶硅作为重要的硅单质材料之一,早期仅用作生产单晶硅的原料。从 20 世纪 60 年代开始,多晶硅薄膜才逐渐应用于微电子领域,成为制作 IC 中的 MOS 管栅极、互连线、桥接线及电容器极板的重要材料。

在压阻传感器方面,与单晶硅相比,多晶硅薄膜器件无需 p-n 结衬底隔离,可实现高温工作;与绝缘体上单晶硅(SOI )相比,其具有工艺简单、制造成本低的优势。但是,普通多晶硅压阻传感器灵敏度偏低,温度系数较高。多晶硅薄膜淀积方法很多,其中CVD 法凭借其工艺简单、成膜质量高、可批量生产等优点得到广泛应用。目前,LPCVD 法是多数商用传感器制作多晶硅电阻的首选工艺,主要基于硅烷的热分解或卤硅烷的氢还原反应。影响LPCVD 法成膜质量的因素主要为淀积温度、硅烷浓度和反应压强,而淀积速率取决于淀积温度和SiH 4流量。随着反应的进行,SiH 4浓度沿气流方向逐渐递减,使样品片间均一性变差。虽然可采用温度梯度补偿,抵消SiH 4损耗的影响,但是温度的微小变化,仍会改变淀积速率,造成片间均一性变差。研究表明,在其他条件不变情况下,淀积温度每改变1°C ,淀积速率就变化5%~5.5%。此外,片内均一性也受样品温度分布及表面气体流动模式的影响。当样片受热不均、与炉管不共心或放置不当时,片内均一性就会下降。一般来说,片内误差在淀积速率较低时约为4%,在淀积速率较高时可达20%。

现在有一种铝诱导晶化法,是一种在玻璃等廉价衬底上低温制备大晶粒、高结晶质量的多晶硅薄膜的新方法。它所制备的多晶硅薄膜具有非常强的(111)择优取向,而 Si (111)和 BaSi 2的晶格错配率仅为 1%。BaSi 2晶体的禁带宽度为 1.5eV ,在 1.5eV 时的光吸收系数比晶硅高两个数量级,因此其是很有潜力的太阳电池材料。

3. 简述双极晶体管电流放大系数随频率变化的原因

晶体管有高频管和低频管之分,一般来说低频管只能用在3MC 以下的频率范围;而高频管则可以用到几十或者几百MC 的高频范围,有时称超过75MC 的管子为超高频晶体管。下图是电流放大系数随频率变化的关系图,由图可看出频率每提高一倍,电流放大系数下降一半。

晶体管的共射极电流放大系数β与信号频率f 间的关系为: 式中,β0为低频是的电流放大系数,f β为共射极的截止频率。特征频率f T 是晶体管可以

起电流放大作用的最高频率的限度,是共射极电路设计的一个重要依据,

,f T 也被称为“增益宽带乘积”。因为β反映了晶体管对电流的增益作用,f 代表了从低频起到某一频率f 的频带宽度。所以β和f 的乘积就代表了增益带宽乘积。

晶体管的电流放大系数随讯号频率增高而下降,有如下四种原因:

1、发射结势垒电容的充放电引起发射效率的下降。根据晶体管的等效电路,如下图所示。PN 结的势垒电容是并联在PN 结电阻上的。交流讯号i e 的一部分流过势垒电容C T ,它不参加基区输运。因此使注入到基区的电子扩散流在总电流中的比例下降了。频率越高,C T 容抗越小,通过C T 的电流越大,电流放大系数就越小。

2、基区渡越时间使基区输运系数下降。扩散通过基区的少子具有与其有效质量及迁移率相关联的一定的惯性,如果加到发射结上的电压的频率不断的增加,载流子对外讯号就不能瞬间响应。其结果造成物理滞后,使复合增加,电流增益下降。

3、集电极势垒渡越时间使电流放大系数下降。基区中的少子输运到集电结边界后,还要越过集电结势垒区,才能到达集电区。因此在高频讯号下,必将引起势垒区中电荷积累的迅速变化,所以需要有部分少子电流去提供这一积累,使越过势垒区能到达集电区的少子数目比由基区输运来的少了。因此使电流放大系数下降了。

4、集电结势垒电容的影响。和发射结相似,集电结还存在势垒电容C T 和集电极体电阻r ce ,所以电流越过集电结后还不能全部变成有用的i c ,有一部分还要对势垒电容C T 充放电,引起电流放大系数的下降和电流的延迟。

计算:

发射效率为

: 基区输运系数为: 共基极电流增益:

基区扩散长度为: L p =D P p =?10-7cm =10-3cm

L 同理: E =D E E =10-4cm

因为

<1>

所以,当w/Lp <1时,i ep="ICP">

所以:

所以:

范文五:适用于深亚微米CMOS器件的Ni自对准硅化物工艺的研究(可编辑)

适用于深亚微米CMOS器件的Ni自对准硅化物工艺的研

究

长春理工大学

硕士学位论文

适用于深亚微米CMOS器件的Ni自对准硅化物工艺的研究 姓名:王大海

申请学位级别:硕士

专业:凝聚态物理

指导教师:万春明;徐秋霞

20031201摘 要

本论文对适用于深亚微米器件的镍自对准硅化物工艺进行 了深入的研究。随着器件尺寸的进一步缩减,与传统的、自对准 硅化物相比,自对准硅化物更能适用于器件对硅化物的要求。 文中详细的阐述了采用/和//结构通过在硅单晶

衬底上制备薄膜的方法。文中对/扣//的热反应特性 以及薄膜的形成规律进行了详细的研究。制备了优质的硅化物 浅结二极管。分析了.浅结反向漏电流产生的机理,研究了不 同的工艺条件对浅结反向漏电流的影响。在优化工艺的务件下,获得的 镍自对准硅化物浅结的对于结深为的结反向漏电流密 度可以达到.一/。实验结果表明,本工艺完全适用于

超深亚微米器件甚至纳米器件对硅化物的要求。

关键词:深亚微米器件,镍自对准硅化物工艺,薄膜

?浅结,反向漏电流 ?

. ...

? ? / .

小/ . . ? / 悄/

.

; .. .. . .~,

.

?

.

,

:

,

,

,

第一章.绪论

.引言

年,美国 社/、等人发明了人类历史

上第一个晶体管川“,标志着现代半导体工业的开始。经过约半个世纪 的迅速发展,作为当今信息世界核心和物质基础的半导体工业已成为一 乙美圆的支柱型产业?。和历史上曾经辉煌的其它

个年产值高达

产业不同的是,半导体工业严重依赖于其技术基础一一微电子技术,特 别是集成电路的高速进步‘州。

自从与在年制作出第一个金属氧化物半导体场,

效应晶体管..

,于年发明集成电路,

【『,在年引入平面艺和年和发表

技术主要是互补技

第一个器件以来”】,平面

术已成了发展的主流技术。近半个世纪的微电子技术发展史也就是平 面

的进化史,其特征表现为不断缩小晶体管和电路连线

的尺寸,以使集成电路获得更高的集成度,更好的性能和更小的功耗。 英特尔的在年对 的发展状况进行了总结,提出著

名的‘‘摩尔定律”,即 的特征尺寸每个月缩小%,

集成度相应提高一倍,同时单元电路的功耗和功能/成本比随之而下降。 回顾微电子技术从发展到今天,每一次技术的革新都能够和“摩尔 定律”很好的吻合,并且每一个技术节点都能够与的预测基本吻

合。并且,随着技术的不断进步,器件栅长甚至出现加速等比例 的趋势:例如,按照 年预测,年

缩小

器件的栅长为,而 年预测,年器件的栅长为,

可以看到,从年到年短短的两年时间里,对于栅长的预测缩 短了一半。

随着微电子技术的快速发展,的特征尺寸不断减小。器件特征 尺寸的减小有利于功耗的减小、速度的加快、集成度的提高。但是一些 影响器件性能进一步提高的问题也随之出现。例如栅介质的等效氧化层厚度,

最大的栅电极电阻,最大/之间的接触电阻,源漏扩展

区的薄层电阻等。如果栅电阻增加,将引起延迟增加,降低器件的 作速度:而源/漏串连电阻的增加,使上的压降增大,造成器件驱 动能力的下降,功耗增大。为了解决源/漏串连电阻和多晶硅串连电阻 对电路性能的影响,引入了硅化物自对准工艺。

另外,在超大规模集成电路中,随着电路规模的进一步增大,器 件和薄膜尺寸横向和纵向都将按等比例地缩小,作为互连材料的多晶硅 薄膜,其较高的电阻率已经戍为提高集成电路速度的限制因素之一。延 迟时间常数与电阻率和方块电阻有如下的关系:

:上.业:盟:口盈

。。。

式中:口:方块电阻 ,:互连引线长度

: :

引线的厚度 引线的宽度

多晶硅互连引线下面的绝缘层的介电常数

。。:

多晶硅互连引线下面的绝缘层的厚度

。:

从上式可以看出,延迟时间常数与方块电阻成正比,与引线长 度,的平方成正比,与绝缘层的厚度成反比。考虑到边缘效应,延迟时 间常数也将随着线宽的减小而增加。而作为互连材料的多晶硅薄膜 由于自身杂质固溶度的限制,其电阻率不能进一步减小以适应延迟时间 常数,从而限制了特征尺寸的进一步减小。为了克服这一限制,人 们对发展低电阻率的难熔金属硅化物及其互连技术产生了浓厚的兴趣。 广泛的讲,元素周期表中超过半数的元素都可以与硅反应生成一种 或多种硅化物,如表?所示,但是适用于集成电路使用的必须具有下 列的性质:低电阻率、易于生成、易于刻蚀、可氧化并且生成的氧化层 绝缘性能好、应力小,附着性好、表面光滑、与整个集成电路工艺相见 容、与最后的金属铝不易发生反应、不引起另外的污染等等。适应于上 述要求的主要是第四、五、六主族的难熔金属硅化物和第八族的亚贵金 属硅化物?。

岳

罚

占

搿

占

. 咯 吆 ,

并

蠹

牙

鬯

鬯

兽

蛊 一 蛊

.

苗

嗡

哩

唔

苣

苣 苣 皇

。

萌

咯

孑

岂

窒

岂

窭

皇

. . ? .: 强

电

啥 呕 塥

嘧 屹 占

鬯

士

亭

亭 至

? .:

.

苗 . 苷

电

芒

鲞

詈

亭

声

?

礁

鬯

薯

暑

时

一

苗

壹

岛

.硅化物在栅结构中的应用

金属硅化物最初应用到栅介质上有两种方法:一种是将金属硅化物

直接用作栅互连材料来代替重掺杂多晶硅,这种方式的难点在于如何保

持栅氧化层的稳定性低的应力、较少的界面态、硅化物表面氧化层 的形成、以及硅化物与栅氧化层之间良好的粘附性;另一种是采用硅化 物/掺杂多晶硅复合栅结构,口结构。后者由于硅化物下面的多 晶硅原子在高温氧化气氛中可以迅速穿过硅化物并在其表面形成氧化 层,从而比较容易形成高质量的自钝化层以防止多晶硅中杂质的挥发; 并且硅化物/掺杂多晶硅复合栅结构具有良好的工艺兼容性,保持了多 晶硅与二氧化硅之问良好的界面,因而得到了广泛的研究。 .硅化物在接触孔源/漏上的应用

随着艺技术的不断进步,到六十年代,硅化物被首次提出用于 硅接触孔,以降低因接触孔尺寸变小,表面活性杂质浓度降低而导致的 接触电阻的增加。在这种情况下,硅化物采用金属与硅讨底热反应的方 法生成。当器件尺寸进一步减小到深亚微米阶段时,’寄生串联 电阻成为器件性能进一步提高的障碍。而寄生串联电阻主要由 。

接触电阻、薄层电阻、电流扩展电阻和电流积累电阻四部分组成【 为了同时克服源/满及多晶硅栅的接触电阻和薄层电阻对器件性能的影 响,硅化物自对准工艺应运而生。硅化物自对准工艺不仅同时降低了多 晶硅和源/漏区的薄层电阻和接触电阻,提高了连线能力,而且简化了 工艺。

硅化物薄膜的制备

制备硅化物的方法有很多,目前最重要的有:

共溅射方法。按要求的原子比,从两个不同元素的靶逐次溅射难

熔金属并口硅,组成精细的多层结构,然后退火形成 硅化物。

共蒸发方法。按一定的原子比,同时蒸发难熔金属和硅,或者同 共溅射一样,逐次蒸发难熔金属和硅,形成多层结构,然后退火 形成硅化物。

合金靶溅射。即以一定的原子数比例,将难熔金属和硅粉末热压 形成合金靶然后直接溅射到硅多晶硅或衬底上。

自对准硅化物工艺:即溅射或蒸发单层难熔金属于多晶硅或硅衬 底上,在退火过程中,难熔金属与硅多晶硅衬底反应形成硅 化物,而氧化层上的金属薄膜用选择性腐蚀法去净。 化学气相淀积法。包括:、和等。

其中、溅射金属薄膜并退火反应形成硅化物和化学汽相淀 积硅化物是两种应用最广泛的硅化物形成方法。

.传统自对准硅化物工艺及其存在的问题

在自对准硅化物艺中,硅化物薄膜的电阻率、热稳定性、耗硅量 硅化物浅结的性能、选择性腐蚀性能等是衡量自对准硅化物工艺的 决定性因素。

考虑以上的因素,仍然是制作自对准工艺的首选材料。另外 具有萃取自然氧化层的能力,因而可以有效的根除源漏区和多晶硅栅表 面上的自然氧化层,使反应开始于一个新鲜、平整、原始的界面。但随 着器件尺寸进一步减小到深亚微米阶段,由于材料本身的特性, ?已经带来了一系列严重的问题。其主要表现为【】:

的热生长动力学表明,硅是主动扩散源,出.艺不当有 可能在侧墙上形成硅化物残留,使源/漏区发生连通,造成器件的 失效。即“桥连”失效。如图.所示。

图

制备过程中的“桥连”示意图

形成温度较高,形成温度范围窄,实际工艺中不易控制。 非常明显的线宽效应。即随着线宽的减小,硅化物薄层电阻急剧 上升。在线宽时,薄膜的方块电阻随线宽的减小稍有增加,但基本上没有明显

变化;在线宽?.时,

薄膜的方块电阻随线宽的减小而明显增加;在线宽?.时, 薄膜的方块电阻随线宽的减小而急剧增加。透射电子 显微镜分析表明:在线宽??.时,薄膜的方块

电阻随线宽的减小而明显增加是由于高阻态的相到低阻态的 相的不完全转变所致。即除相外,还有相的存在。 电子衍射分析表明,大晶粒在.蝉左右,具有结构;而 小晶粒在.左右,具有结构。当线宽./??.岬时, 薄膜完全只有高阻态的相组成。这是因为的成核发 生在个晶粒的交叉处,所以,当线宽.?时、由于相成核 极其困难,导致大量的高阻态相的存在,使连线电阻不断升高; 当线宽.“时,由于凝聚效应,使连线电阻进一步急剧升高。 而进一步的高温退火则加剧了薄膜的戍团现象

,从而导致薄层电阻的更进一步上升。特别是

线宽小于.微米后,薄膜的常规.薄层电阻急剧

升高,严重的阻碍了它的应用。

在薄膜的形成过程中,会有明显的杂质外扩散发生,从而导 致界面处杂质浓度的降低,使接触电阻升高。

基于上述的原因,人们把目光投向了另一种硅化物薄膜薄 膜。其做为薄膜的替代材料,具有以下的优点:

的热生长动力学表明,硅是主动扩散源,从而有利于“桥连” 的减少。如图.所示。

图.制备过程中的抑制“桥连”示意图尤其是殳.有窄线宽效应,即与不同,

的薄层电阻

没有随线宽减小而增大的效应。

但随着器件尺寸进,一步减小到超深亚微米阶段,由于材料本身的特 性,.已经带来了一系列严重的问题。其主要表现为: 薄膜的热稳定性较差。

薄膜在形成过程中所需要的温度高,从而增强了杂质的再分 布,而影响器件的性能。

尤其严重的是常规的薄膜在形成过程中所消耗的硅量多,往 往造成浅结漏电大,且容易形成“空洞”,而影响器件的性能。 如图.所示。

戳‖。

舅?趣一:

脚.

备过程中产生“空洞”示意图

.新兴的自对准硅化物工艺

为了进一步满足器件尺寸减小到超深亚微米对自对准硅化物 的要求,人们把目光转向了具有上述优点并且在硅化物薄膜形成过 程中所消耗的硅量更少?自对准硅化物工艺。与传统的自对准硅 化物工艺和自对准硅化物相比,自对准硅化物有以下的 优点:

在薄膜的形成过程中的温度较低。一般在?空..

间,典型的为~。之间

在薄膜的形成过程中所消耗的硅量也比较小,有利于浅结 的制备。

在薄膜的形成过程中,由于是主动扩散源,从而有利于 “桥连”的减少。

尤其是没有窄线宽效应,即与不同,的薄层电阻

没有随线宽减小而增大的效应。这是它应用于超深亚. 器件的最大优越性之一。

薄膜的应力较小。

.

自对准硅化物工艺目前国内外的研究现状

国外关于自对准硅化物的研究在九十年代中期就已经开始了。到 现在为止,有许多的实验室和研究机构在进行研究。其工艺技术已经基 本上成熟,公司预测在年自对准硅化物工艺可以走出实验

室应用到大规模的生产中。而国内关于自对准硅化物的研究很少,只 有复旦大学、清华大学报道过相关的薄膜的性能和制备技术,但是 其所应用的技术手段乖传统的集成电路工艺不兼容。本论文的研究工作 在国家项目“?纳米中新器件,新工艺研究”支持下进行。 徐秋霞研究员是上述研究项目的课题负责人。本研究工作在国内首先全 面展开对自对准硅化物工艺的研究,包括薄膜性能理论研究,一 硅化物浅结的结构设计及其版图设计,薄膜的制备技术研究, 薄膜的物理及电子特性分析等一系列内容,力图建立起适应于集成电路 制作中可实用化的先进技术。在通过关键工艺研究的基础上成功制备了 高质量的薄膜,并对其浅结的电学特性进行了详细分析,并和传统 的自对准硅化物技术进行对比,最后优化了工艺技术参数,研发出了标 准的、与传统的集成电路制造技术相兼容的自对准硅化物工艺技术。 填补了国内的技术空白,为光匕艺模块的建立和向大生产转移奠定了 基础。

.论文的内容安排

本论文的内容安排按照理论研究、设计、制作,再分析总结的一般 页序。首先在第章对硅化物和自对准硅化物艺进行了简单的介绍: 第章对薄膜的性能进行了理论分析,重点阐壶.薄膜自身的性能 及其在器件尺寸缩小的过程中所具备的优点。第章为薄膜的制备 技术研究,通过溅射金属薄膜并退火反应形成硅化物的方法制备了薄膜,研

究了不同的工艺条件对薄膜性能的影响,优化了艺参数,

制备了优质的薄膜,这是本文的第一个重点;第章通:过自对准

硅化物浅结的?生能来检验薄膜的性能,描述了设计浅结的方法和过 程,包括结构设计、器件参数分析、重要结构参数的确定、硅化物浅结 的制备及其性能分析等,这是本文的第二个重点;最后在第章给出结 论。

.本章小结

本章所介绍的主要内容包括:

?硅化物工艺的提出自对准硅化物工艺的产生

?随着器件尺寸的进一步缩减,传统自对准硅化物存在的问题 ?新兴的自对准硅化物的优点

?自对准硅化物国内外的研究现状

?本论丈的内容安排

第二章.新兴材料一一

.

薄膜与的反应

在与的反应过程中所存在的环境实际上是一个富硅的环境,因 此在不同的温度与可形成不同的相:、、。如表

.所示根据分析

表?不同种类硅化物薄膜的性能

薄膜电阻率血?

体电阻率艘?卅

生成物相

退火温度

、

小于

,

?

小于大于 ~

大干 一

在不同的相中,薄膜的电阻率最低,可以满足器件尺寸进一步

减小到深亚微米阶段时的需要。典型/薄膜的晶体结构为斜方晶系

的,其晶格常数为:.,.,.;另外,还存在正方晶系的 薄,其晶格常数为:口.,.

.

薄膜接触势垒高度

表.为不同的硅化物薄膜的接触势垒高度。 表.不同的硅化物薄膜的接触势垒高度例 硅化物

势垒高度电子

势垒高度空穴

. .

.

.。

..

由表可知,对于空穴来说,与和的硅化物相比,的硅化物具

有比较低的势垒高度,这对于一个型的掺杂层来说具有很大的优越性 由于与型的掺杂层的接触电阻通常都高于型的掺杂层。 .

薄膜形成过程中的耗硅量

当器件尺寸进一步减小到深亚微米阶段时,与之相对应的源漏结的 结深也随之减小到左右。这样,如果在硅化物的形成过程中所消 耗的硅多,硅化物与硅的界面距离结的边界就很近,很容易造成结 的漏电,严重的造成的穿透,从而影响整个器件的性能。如图.所 示【。

圉.硅化物的形成过程中所消耗的硅量示意图

表?为不同的难熔金属在形成硅化物时所消耗的硅量。有袁中可 以看到,传统的和硅化物相比,的硅化物所消耗的硅量最小, 对浅结的影响也就最小叫。表.不同的难熔金属在形成硅化物时所消耗的硅

量

原于体积

形成硅化物时每

每金属形成

硅化物

金属

硅化物的厚度

金属所消耗的硅量

. .

.

. . , . 一

.

.

..

, . .. .

.

. . .

.

.

.

.

.

.

.

.

.

.

.

.

~.

..

.本章小结

本章的主要内容包括:不同种类硅化物薄膜的性能不同的硅化物薄膜的接触

势垒高度

?

不同的难熔金属在形成硅化物时所消耗的硅量薄膜的制备及工艺优化 第三章.

为了.自对准工艺与深亚微米器件制备技术具有良好的工艺兼 容性,我们选择了溅射金属薄膜并通过快速热退火反应来形成 硅化物的方法来完成薄膜的制备。自对准硅化物工艺的流程如 下。

金属薄膜的溅射一一超声清洗? 一选择性腐蚀

.溅射前硅片表厩的处理

由于贵重金属氧化物的生成热低于二氧化硅的生成热,不具有分 解二氧化硅的能力。因此硅衬底表面的自然氧化层会阻碍与臼々反 应,使二者的反应不能在整个界面均匀地进行,从而造成/界面的 乎整度变差,增加了尖钉的可能性,从而影响浅结的反向作 性能。

为了获得尽可能新鲜的硅表面,我们采用了以下的清洗条件: 用常规清洗液来去除有机物、金属离子、原子等;

用专用的/洗液漂秒以去除自然氧化层:

然后在氮气的保护下甩干后,立即进入溅射腔内,尽量缩短 片子在空气中暴露的时间,避免自然氧化层的形成。

.金属薄膜的淀积条件和厚度控制

我们使用日本 ,磁控管平面溅射台做金属

膜的溅射。由于溅射台没有膜厚的实时控制功能,我们只有通过实验来 确定一定溅射条件下的金属膜溅射速率,再通过溅射时间来控制金属膜 的厚度。为了较好的控制金属薄膜的厚度,维持工艺上的可重复性,又 兼顾金属薄膜的质量,我们希望在溅射的时候,溅射的速率比较慢才好。 由于与反应需要消耗的是厚度的.倍,所以对于左右的

浅结上的薄膜所消耗的硅量不应大于,为此我们在后面的实验 中设计.金属薄膜的厚度应该在?,生成的薄膜在理论上

在?。

通过以前大量的实验,在优化了射频功率、气体流量、本底真空、预热温度

等工艺参数的基础上,开发了下面的溅射条件来制备优质的金 属薄膜:

溅射功率:??

衬底温度:?%

本底真空:~一

??

气体流量:

??

溅射真空:一

通过以前的实验,结果发现:在溅射之前对衬底材料做一次腔内的 在线退火适当的退火温度,金属薄膜的完整性和附着性有明显的改 善。认为原因有以下两点:

腔内在线退火提高了腔体内的真空度。

退火以后的衬底温度比室温要高,降低了界面能,可以使溅射到 表面的金属原子的迁移能力增强,有利于在衬底上寻找最低的势 能位置,降低界面处和薄膜内部的庄力,提高了/的亲和力, 提高了薄膜的完整性和附着性。

.

薄膜的制备工艺研究以及工艺参数的优化

.. 薄膜形成温度的优化

由于在与的反应过程中所存在的环境实际上是一个富硅的环 境,因此在不同的温度与

形成不同的相:、、。

分析表明:温度小于。时,形成的主要为、相;温度

小于。而大于’时,形成的主要为相;温度大于。时, 形成的主要为相。在不同的相中,薄膜的电阻率最低,因此可 以根据方块电阻大小的变化来判断是否发生了相变。但是,方块电阻和 上层金属薄膜的厚度、衬底类型有关。为此,我们设计了以下的试验方

案来优化薄膜的形成温度。

首先,固定金属膜的厚度、退火时间和衬底类型的条件下,; ?为基础,每。为间隔,研究薄膜的薄层电阻随快速热退火温度 的变化规律。在这里我的衬底为:电阻率在~.掰、晶向为 的型英寸硅片,快速热退火实验是在清华微电子所研制的红外快速热退火设

备上完成的。我们对退火后的样品首先利用

四探针进行方块电阻的测试,然后对样品进行选择性腐蚀,再一次的利 用四探针测试方块电阻,最后对方块电阻有明显差异的样品进行 分析。在这里我们选择的薄膜厚度为金属薄膜厚度的上限,因 为在理论上,的金属薄膜可以生成.厚薄膜。图.给

出了的金属薄膜在同一时间,不同的退火温度下利用四探针所 测得的薄层方块电阻随退火温度的变化关系图。

图.薄层方块电阻与后退火温度关系图。

薄膜,固定时间为秒,选择性腐蚀后

由图中可以看出:在。和。之间,薄膜的方块电阻降到最低, 根据我们上面的分析,我们可以初步的确定:在这个温度范围内形成的 是薄膜。随着温度的升高,薄膜的方块电阻也随之变大,即发生了 薄膜逐渐向转变。由于我们的退火设备最低温度只能降低到 。,因此,我们只对。以上的方块电阻最低和最高的样品做了 分析,分析结果表明,方块电阻最低的薄膜的主要成分是,而 方块电阻最高的薄膜的主要成分是。通过方块电阻和的测试 结果,我们可以初步确定薄膜的形成温度。

。样品的图 ”样品的图 笔

’样品的图 图.不同方块电阻薄膜的衍射圈

表.不同样品的峰值样品编号 峰值编号

. 】 . ..

. . . . .

.

. . . . . . . . . . . . . . . . .

,

. .

. .

.其中:样品。:温度:?,时间:;

样品”:温度:??,时间:秒

样品”:温度:???,时问:秒

通过与标准的图谱相比,我们发现: .样品的号峰、。样品的号峰以及样品的号峰与斜方晶系的

在和晶向上自基本相同::.,

.;::.,:.。

.

样品的号峰、。样品的号峰以及样品的号峰与斜方晶系的

在扣晶向上基本相同’::.,.;::.,:.。 .样品的号峰与斜方晶系的在晶向上的基本相同 ::.,:.;样品的、峰与斜方晶系

的在晶向上的基本相同::.,:

.;。样品的峰与正方晶系的在晶向上的 基本相同::.,:.。

.“样品的号峰与立方晶在晶向上的基本相同 ::.,:.;“样品的号峰与斜方晶系的 在晶向上的基本相同::.,:.: 样品的号峰与方晶系的在晶向上的基本相同 ::.,:.;“样品的号峰与斜方晶系的

在晶向上.基本相同::.,:.:

“样品的、峰与斜方晶系的在晶向的基本相同

’::.,:.。

通过对的分析,我们可以得出以下的结论:

.在我们所研究的退火温度的范围内,金属薄膜与反应生成 薄膜。

.在这个温度和时间的条件备的薄膜是多晶的。

.随着退火温度的上升至。,开始发生薄膜逐渐向薄 膜转变,检测到存在。这和我们方块电阻的测试结果是 ’

一致的。

为了进一步研究我们所制备的薄膜的性能,我们对样品进行 了电镜分析。图.为样品的图。

图 样品的图

通过图,我们可以清楚的看到所制备的薄膜为多晶膜。在 图.中,我们可以看到有一小部分的薄膜的具有一定的晶向,但 是面积很小。从总体上来看,薄膜还是多晶的。

图.薄层方块电阻与后退火温度关系图。,选择性腐蚀后其次,为了进一步确

定薄膜的形成温度,我们在同样的衬底

条件下对不同厚度的金属薄膜进行了同样的热退火。图.给出了不 同厚度的佥属薄膜在同一时间,不同的退火温度下利用四探针所测得 的薄层方块电阻。

从图中可以看出,不同厚度的薄膜的方块电阻也是在温度为 ?。之间是最小的,并且随着温度的上升,方块电阻先下降至最小 值后再逐渐增大。这样我们可以确定薄膜的形成温度在? 之间。随后的结果也证明了这一点。

从图.中,我们发现随着上层金属厚度的减小,所形成硅化物的 热稳定性逐渐变差。具体为:随着温度上升到??,对于

厚的薄膜来说,退火以后的薄层方块电阻迅速增大,即出现了由 向:相的转变。而对于厚的薄膜来说,退火以后的薄层方块 电阻在这个温度范围变化不大;至到?以上时,才出现了由向 相的转变。

..

薄膜形成时间的优化

为了考察上层金属薄膜是否已经完全与反应,我们对的

金属薄膜在同一衬底类型,在上述已经确定的退火温度的条件下进行了 图薄层方块电阻与后退足时间关系图。,选择性腐蚀后不同的退火时间下薄

膜方块电阻的测量。图.给出了的金属薄

膜在同一退火温度,不同的退火时间下利用四探针所测得的薄层方块电 阻。

由图可以看出,在固定温度下,退火时间在后,薄膜的方块 电阻基本上没有太大的变化,如果排除测试仪器的误差,可以判定上层 金属已经完全反应了。而在退火温度为时,随着退火时间的增加, 薄膜的方块电阻逐渐减小;在时间为秒以后,方块电阻随时问不在变

化。

同样的,我们也对不同厚度的金属薄膜进行了同样条件下的后退火 处理,得到了同样的结果。图.出了不同厚度的金属薄膜在同一退 火温度,不同的退火时间下利用四探针所测得的薄层方块电阻。 图.层方块电阻与后退火时间关系图。同一退火温度,选择性腐蚀后 不同衬底类型上薄膜的方块电阻

在实际双.阱器件艺中,管和管的源漏区是同一衬底

的不同的掺杂类型,而源漏和栅极又是不同的衬底源漏为, 而栅极多为掺杂的多晶硅,因此,研究不同衬底类型上薄膜的方 块电阻具有重要的意义。

如图.薄膜的方块电阻与不同掺杂的单晶硅的关系图。从图 中可以看出,在整个温度范围中,薄膜的方块电阻的变化趋势基本 上是一样的。即:在。以下时,随着温度的升高,方决电阻增加; 而在?与。之间时,方块电阻迅速下降;。到’之间,方 块电阻最小且变化不大;?以上,方块电阻迅速增大。这种变化主 要是由于在温度升高的过程中,形成了具有不同电阻率的不同的硅化物 相所造成的。刚开始时生成相,电阻率较大;随后为相,电阻 率最小;最后为相,电阻率最大。虽然薄膜的方块电阻的变化 趋势是一样的,但是,对于不同厚度的薄膜来说,三种不同的衬底类 型上分别掺杂、、其方块电阻在整个温度范围内有明

显的不同。对于的金属薄膜,所获得薄膜的方块电阻:掺 图.薄膜的方块电阻与不同掺杂的单晶硅的关系图

杂的最大、次之、最小;而对于的薄膜来说,三者基本一致。 由此可见,随着薄膜厚度的减小,不同的衬底类型对硅化物方块电阻 的影响明显增强。造成这种现象的原因可能有以下两个方面:一是随着 上层金属薄膜厚度的减小,相应的生成薄膜的厚度也在减小;二是 随着薄膜厚度的减小,衬底中的杂质作用显著起来,一方面是杂质 本身对薄膜方块电阻的影响,另一方面是杂质影响了薄膜的形成过程,进而

影响了薄膜的方块电阻。

对于不同掺杂类型的多晶硅薄膜来说,以上所获得薄膜

的方块电阻的变化与掺杂的衬底大致相同;而在?以下,随 着温度的升高,薄膜的方块电阻反而降低。造成这种现象的原因还 在进一步的研究中。

在这里,需要说明一点的是,由于我设备自身的限制,我们 的退火温度只能降低到?左右,因?以下的结果是根据参考文 献得到的。

..

薄膜热稳定性的研究

薄膜的热稳定性是评价其性能的一个重要指标。器件尺寸的不 断缩减电路规模的不断扩大都要求薄膜具有很优良的热稳定性。 但是,一方面,随着线宽的减小,薄膜的相转变温度由低电阻率 的井向高电阻率?/相的转变温度会不断降低,从而使薄膜的 方块电阻显著增加而影响器件的性能。另一方面,在硅化物的形成过程 中,尽管在退火的过程中有氮气的保护,但是还是会引起硅化物薄膜的

氧化,即:在形成的薄膜中有大量的氧存在;氧原于的存在一方面 是薄膜的方块电阻增大,另一方面也是薄膜的热稳定性变差。因此,怎 样提高薄膜的热稳定性已成为当前研究的热点。 目前,主要有以下两种方法来提高薄膜的热稳定性。 通过注入来改善薄膜的品质‘

其机理为:注入是在薄膜的溅射前进行的。注入后溅射金属 薄膜,然后进行形成硅化物薄膜。的分析表明注入的 主要分布在薄膜晶界的周围,有助于改变晶界的能量:而且, 注八的也可以和或反映生成氮化物而改变界面能,从而抑 制和延迟成团而提高薄膜的热稳定性。我们

对此没有进行进一步的研究。

利用、或覆盖层来改善薄膜的品质;

通常的艺为:在金属薄膜溅射完以后直接在其表面溅射一层 、或者的覆盖层,然后进行形成硅化物薄膜。

我们重点对/双层薄膜的性能进行了研究。我们之所以选择 交为上层的覆盖金属薄膜,是因为与、’金属薄膜相比,金属 薄膜具有更好的附着性和抗氧化性。

图.为不同厚度的双层金属薄膜/与不同厚度的单层金属薄膜 在不同逞火温度下的方块电阻变化图

由图中可以看出,/层金属薄膜所形成的硅化物薄膜与弹 层金属薄膜所形成的硅化物相比,不但热稳定性有了明显的改善我们 这里是指由相向相转变的温度,而且薄膜的方块电阻也进一

步的减小。分析原因,我们认为,上层覆盖的金属薄膜,一方 面抑制了硅化物在形成过程中的氧原子的入侵而造成的薄膜氧化:另一 方面薄膜的掺杂作用也抑制了的形成。这是因为:的形戍 过程实际上是一个晶核控制过程。当反应的自由能

改变量不能与界面能的增加量主要是由于新相物质的形成 /小.仃/相平衡时,这种晶核控制反应便可

以发生,而晶核的有效激活能正比于

/?。薄膜的掺杂

作用有利于

的增加和的减小。从而提高了晶核的有效激活能?

而使成核的数量下降,降低了的形成几率,从而提高薄膜 的热稳定性。.

薄膜厚度的优化

..

薄膜厚度的优化

在自对准硅化物工艺中,所形成的硅化物薄膜的厚度是评价硅化物 薄膜性能的一个重要指标。一方面,我们希望硅化物薄膜的厚度越厚越 好,这样所形成的硅化物薄膜的方块电阻就越小,串连电阻就减小,电 路的速度就可以进一步的提高;另一方面,随着器件尺寸的不断缩减, 源漏结的结深也越来越浅,较厚的硅化物薄膜所消耗的硅膜也比较多, 这样很容易引起浅结漏电的增加,从而引起整个器件性能的恶化。 图.为不同的自对准硅化物工艺、、中每单位厚度的上层金属

所消耗的硅膜厚度以及生成相应硅化物薄膜的厚度的示意图。 由图中可以看出:每单位厚度的金属薄膜,所消耗的最多, 次之,最少;其分别为:.、.、.,相

对应的硅化物薄膜的厚度分别为:.、.、.。

随着器件尺寸的不断缩减,较少耗量々自对准硅化物工艺相对于 和来讲,具有更大的优势。尤其是对于近几年来非常热门并且有可能 取代体硅的器件和技术而言,极其重要。

研究表明,对々结深,硅化物薄膜的厚度不能超过瓣漏结结 深的一半,否则结的漏电流相当严重。因此,在实际的工艺中,我们在对这两

个方面进行优化以后,选择的上层金属薄膜的厚度在., 这样厚度的薄膜在理论上可以生成.?.々薄膜,同时消耗 撺...的硅膜。

..不同类型的衬底对薄膜厚度的影响

在实验中我们发现,不同类型的衬底材料对所生成的薄膜的厚 度没有影响。我们分别采用了型,~脾.和型

,~脾?两种完全不同的衬底,退火的温度和时间完

全一样。我们通过两个方面来考察生成薄膜的厚度,一是通过 直接观察生成薄膜的厚度,进行比较;二是通过方块电阻的测试来 考察生成薄膜的厚度,因为薄膜的方块电阻和薄膜的厚度直接相 关,可以用下面的公式表示:

,、/

。%

其中::薄膜的电阻率 ,:薄膜的厚度

通过方块电阻的测量,我们发现同一厚度金属薄膜在不同衬底类型 下较低的掺杂浓度所获得的薄膜厚度基本是一致的。

.

薄膜的有效厚度

在实际的器件结构中我们所考察的硅化物薄膜的厚度实际是指的 是硅化物薄膜的有效厚度。定义硅化物薄膜的有效厚度为: %

在这里::硅化物薄膜的横截面;:的宽度。

定义硅化物薄膜的有效厚度的意义在于它能够真正的、有效的反应 出硅化物薄膜的实际厚度。这是因为在不同硅化物形成过程中,由于反 应动力学的不同而引起硅化物薄膜在边缘处和中间部分的厚度是不一 样的。如图

和图.所示。在薄膜的形成过程中,由于是主

动扩散源,在线条边缘处的原子会“主动扩散”到侧墙边缘从而导致 中间区域的原子数目相对减少,从而使边缘处自薄膜变薄。随着 线宽的减小,这种“边缘效应”也在加剧。根据我们定义的硅化物薄膜的有

效厚度,随着线宽的减小,薄膜的有效厚度明显减小,从而使 薄膜的方块电阻明显增大而影响器件的性能。而对于薄膜和 薄膜来说,在其形成过程中,由于和是主动扩散源,在侧墙 上的原子和原子会“主动扩散”到线条边缘处与原子反应形成 薄膜和薄膜,从而使边缘处的薄膜和薄膜变厚,随

着线宽的减小,薄膜和薄膜的有效厚度明显增加,从而使 薄膜和薄膜的方块电阻明显减小而提高器件的性能。 图.为不同硅化物薄膜在不同的线宽下的截面图

和

图.为不同的硅化物工艺中的扩散机制”. 薄膜的选择性腐蚀 我们这里所说的选择性腐蚀是指利用一神腐蚀液将没有完全反应 的盒属和在氧化层上的金属腐蚀除去的同时并不影响硅化物薄膜 的性能。

选择性腐蚀液的选择比将直接影响到硅化物薄膜的性能,进而影响 到这个器件的性能。在这里我们利用和的混合液来做为 薄膜的选择性腐蚀液,腐蚀是的温度为。。没有选用文献上常用的 和?混合液是因为和的混合液也可以做为自对准

硅化物工艺的选择性腐蚀液,一方面工艺兼容,另一方面也可以节约成 本。

在实验之前,我们通过在氧化层上淀积金属薄膜的腐蚀和对 薄膜的腐蚀速度比来检验它的腐蚀效果。如图.为金属薄膜的方块 电阻和薄膜的方块电阻随腐蚀时间的变化图。

图

金属薄膜的方块电阻和薄膜的方块电阻随腐蚀时问的变化图 由图中可以看出,在分钟以后,氧化层上的金属薄膜已经完全被 腐蚀掉了可蹦通过薄层的方块电阻不随时问的变化而变化来决定,并且可以

看出,无论腐蚀时间的长短,薄膜的方块电阻都没有明显

的变化稍微的增加可能是由于腐蚀液稍稍的腐蚀了一些薄膜。 由此可见,我们所选择的腐蚀液还是比较优理想的。

为了进一步考察选择性腐蚀液的性能,以及/’双层薄膜的性能, 我们对双层金属薄膜所形成的硅化物薄膜进行了选择性腐蚀研究。如图 .为不同厚度的双层金属薄膜主要是金属薄膜厚度的不同所形 成的硅化物薄膜的方块电阻与腐蚀时间的关系图。

时问分

图.不同厚度的双层金属薄膜所形成的硅化物薄膜

的方块电阻与腐蚀时问的关系图

由图中可以看出,尽管薄膜的双层金属薄膜主要是金属薄 膜厚度的不同所形成的硅化物薄膜的方决电阻有所不同,但是它们的 方块电阻在选择性腐蚀前后都没有明显的变化。这种结果一方面说明了 金属已经基本上完全参加了反应,另一方面也说明了所选择的选择性 腐蚀液是适合我们工艺技术要求的。.本章小结

本章的主要内容包括:

?优质金属薄膜制备工艺的优化

?薄膜制备工艺参数的优化

?薄膜的性能研究

?薄膜的选择性腐蚀自对准硅化物浅结反向.特性的研究 第四章.

.概述

薄膜在超深亚微米和纳米器件中应用面临的主要问题之一就

是如何改善自对准硅化物浅结的反向.特性。硅化物浅结漏电流 的大小直接决定着硅化物薄膜能否应用在超深亚微米和纳米器件中。与 和的硅化物浅结相比,自对准硅化物浅结具有更小的反向漏电 流。最近几年很多文献就此问题方面的研究做过报道。人们普遍认为 自对准硅化物浅结的漏电主要是由于/界面处的粗糙不平和金 属表面的氧化所引起的。金属表面的氧化我们可以通过在表 面覆盖一层或者来加以克服;但是对于/界面处的粗糙不 平一直没有有效的方法加以克服。但是,在我们的实验中,我们发现除 了两个方面以外,我们还发现了在自对准硅化物浅结中经常出现的 尖钉现象。在下面的浅结的反向特性讨论中,我们将进一 步的讨论上述的问题。

.浅结二极管的优化设计

..浅结二极管的结构设计

通常来说,浅结二极管的反向漏电流有两部分组成:面漏电和线漏 电。可以用下面的公式来表示:

。。。

:二极管的面积;

其中:』?:面漏电密度,

,?:线漏电密度:二极管的周长。

因此,为了考察自对准硅化物浅结反向漏电流的性质,我们设 计了两种不同类型的二极管:一种是为了考察面漏电的圆形二极管,它 们具有不同的面积;另一种是为了考察线漏电的疏状长线条形二极管,

它们具有不同的长度。这样,我们可以通过对这两种二极管的测试采判 断出那一种漏电流是主要的,进而为我们优化工艺条件指明了方向。 由于以前所设计的硅化物浅结二极管的结构是从背面引出测试反向漏电流

的另一个电极,其存在很多不合理的地方。首先,结就必

须用型衬底,而结就必须用型衬底,这样与实际的标

准工艺没有可比性实际的工艺是在同一种类型的衬底上双阱, 然后在阱中做结,而在阱中做结,这里所说的结都是器

件源漏区的结,也就是我们所要形成的硅化物浅结;其次,背面引出 的时候,首先需要对晶片的正面涂胶来保护图形,然后进行背面的刻蚀 减薄主要是去除背面的氧化层、多晶硅等、背面注入不同类型的 结需要注入不同的杂质类型、激活杂质等一系列的工序,增加了 工艺的复杂性;第三,在背面杂质激活的过程中,可能对浅结的 结深产生影响由于浅结的注入条件和背面注入的条件是不一样的; 另外,背面与样品测试台接触的好坏、样品测试台是否洁净等等,这些 因素就不可避免的引起较大的测试误差。针对这样的问题,我们在设计 二极管的结构的时候特意设计了在晶片的上面引出电极。具体的设计 为:我们在和阱中个增加了几个个圆形的接触孔,并且在设计版 图的时候,在结注入的时候即阱上杂质的注入同时注入

阱上的接触孔来形成的接触孔;反之,在结注入的时候即

阱上杂质的注入同时注入阱上的接触孔来形成的接触孔。由 于我们浅结的注入和接触孔的注入是在同样的条件下进行的,因此随后 进行杂质激活的过程不会对浅结的结深产成明显的影响。同时样

品的背面也不周额外的处理,背面与样品测试台接触的好坏、样品测试 台是否洁净这些因素对浅结反向漏电的影响也减到了最小。 我们设计了不同面积和长度的二极管,因此需要相应的接触孔与之 相对应,考虑到版图面积的大小以及对版图面积的充分利用,我们分别 在阱和阱上设计了个接触孔。

..浅结二极管结构参数的分析和确定

在确定了浅结二极管的结构以后,下一步便要确定浅结二极管的参 数,其主要包括:圆形二极管的面积、长线条形二极管的长度、长线条 形二极管线条问的间距、接触孔的面积等。

圆形二极管面积的大小是其反向漏电流大小的决定因素。如果面漏 电密度在整个二板管的面积上均匀分布的,则圆形二极管面积的大小直接决

定其反向漏电流大小,因此较小的面积会得到较小的漏电流。但是, 一方面我们为了考察面漏电是不是硅化物浅结反向漏电的主要原 因,另一方面也为了模拟实际器件中硅化物浅结的面积,我们设计了不 同面积的圆形二极管,其半径分别为:、、、微米,其

中半径为微米的圆形二极管我们设计了两个,这是为了考察我们的 测试结果是不是拥有比较可靠的重复性。我们设计最小的圆形二极管的 半径为微米,是为了在测试的时候比较容易接触。这样,我们便在 阱和阱分布了个不同面积的圆形二极管。

同圆形二极管的设计原理一样,我们分别设计了两组线条数量不一 样的长线条形二极管,其线条长度均为微米,宽度为微米,第一 组有条,第二组有条。线条间的间距为微米。为了更加准确的

测试漏电流,我们将长线条形二极管的测试接触区设计在线条的中间, 第一组的测试长方形的长为微米,宽为微米,第二组的测试长 方形的长为微米,宽为微米。这样的测试区正好可以将所有的 长线条形二极管覆盖起来。

关于接触孔的面积,我们设计了半径为微米的圆形。这样设计 的好处可以将接触孔对漏电流的影响减小到最小,并且也方便了我们测 试时候的接触。

关于接触孔和二极管的距离。根据以往的经验,接触孔和二极管的 距离对浅结二极管的反向漏电流有一定的影响。一方面,如果二者的距 离比较大的话,会在一定程度上减小浅结的漏电流,从而引起测试的误 差;另一方面,如果二者的距离过小,可能在光刻、注入等的时候引起 问题。因此,综合考虑上面的问题以后,我们设计二者的距离为? 微米。

..浅结二极管版图

通过对浅结二板管结构设计结果以及对其结构参数分析的结果,在 综合考虑整个二极管和接触孔的布局以后,我们可以得到浅结二极管的 掩模板图形。我们利用掩模板版图工具.绘制了二极管的版图。其 共有块光刻掩模板,分别为:阱,阱,有源区,

场注入,区注入,区注入。如图.所示。其中,区和区注入掩模板对有源区的覆

盖为个微米,有源区

与孔的间距为个微米,金属对孔的覆盖为个微米。

阱,阱 场注入

?

母

蛰

镄

辫瓣一察

?

?

蹙》

?

区注入 ’区注入

疏状二极管

图 版图.浅结二极管制备 我们在型、~区?的衬底上制备了和

浅结来研究。浅结的反向漏电。结和结的主要制作工

艺见下表。

表.结和‖结的主要制作工艺流程

:

、、\

薄氧

阱注入

,,

,,

阱推进

。?。一 预氧

淀积

光刻有源区 场注入

,。

?\

场氧化 煮

光刻注入区 注入

光刻注入区 注入

,。

快速退火 ?

转载请注明出处范文大全网 » 自对准硅化物工艺研究

用户59671121

用户59671121