范文一:迟滞比较器设计

迟滞比较器设计

1.

设计需求分析:

电路工作描述:例如:当Vin<300mmhg压力对应电压值(如:2.7v)时,vout为低电平,当vin>2.7V时,Vout为高电平,使Q7导通,Valve信号为低电平,气阀打开。直到Vin<>

血压模块过压保护电路模型如下:

说明:图中Vin为压力传感器压力电压值

对应于迟滞比较器的电压传输特性图,VTL=0.3V,VTH=2.7V,VOL=0V,VOH=VCC。

2.电路模型计算:

从电压传输特性图可以看出,Vout=VOL时,Vin=VTH。由运放的虚短和虚断特性可以

得出,其中

Vref=VCCR2

IRin=IRf

VTHVref

RinVrefVOLIRf=

VTH?VrefVref?VOL

=

RinRf

RinRfVrefRin*VOL算式1

VTH=

IRin=

当Vout=VOH时,Vin=VTL,同理可得。

IRin=IRf

VTL?Vref

RinVrefVOHIRf=

Rf

VTLVrefVrefVOH

=

RinRf

RinRfVrefRin*VOH算式2VTL=

RfIRin=

将VTH与VTL相减得:VTH?VTL=

VOHVOL*Rin........算式3

Rf

将需求分析中的VTL=0.3V,VTH=2.7V,VOL=0V,VOH=VCC(实际为3.3V),代入上面的算式3中,可得Rf=1.375Rin..........算式4。将算式4代入算式1中,可得到Vref=1.563V

3.

v

参数选择:

R1,R2电阻的选择:根据Vref=VCC*

R2

R1=1.111*R2。考虑到实际电

R1+R2

R1(KΩ)2.2222.44423.3335.666122.2224.44233.3356.661333.3566.61

阻阻值和功耗方面要求,有以下电阻可选:

R2(KΩ)

22.235.120223051300510

为了达到精确的目的,可以用两个串联电阻代替R1。v

Rin和Rf的选择:根据Rf=1.375*Rin,考虑到实际电阻阻值,功耗,系统电路影响等方面要求,有以下电阻可选:

Rin(KΩ)1.522.22.42224

Rf(KΩ)2.06252.753.0253.330.2533

4.仿真验证:

仿真工具:MultiSIM10.0,电路原理图及仿真结果如下图所示:

从仿真结果来看,R1=33K,R2=30K,Rin=24K和Rf=33K这个参数组合,可以满足电路功能。

范文二:数值比较器设计

实验二:数值比较器设计

一、 实验目的

巩固QuartusII 软件的使用,熟悉Verilog HDL程序结构,学会用文本输入法设计逻辑电路。

二、 数值比较器原理

根据两位二进制数的大小得到对应的比较结果,其电路示意图及电路特性表为:

比较器电路示意图 比较器特性表

三、 程序

Module bijiao(A,B,Ys,Ye,Yb);

Input A,B;

Output Ys,Ye,Yb;

Reg Ys,Ye,Yb;

Always@(AorB)

If(A>B)

Begin

Ys=0;

Ye=0;

Yb=1;

End

Else if(A=B)

Begin

Ys=0;

Ye=1;

Yb=0;

End

Else

Begin

Ys=1;

Ye=0;

Y=0;

End

End moudle

四、 仿真结果

五、 实验总结

这个实验让我理清了思路,让我不再迷茫,让我的基础更扎实了,让我熟悉了数据比较起的原理,并熟悉了程序,但还是在第一次的时候错误百出,所以我还要勤加努力,相信勤能补拙。

范文三:比较器设计分析

rotarapmoUCDA

第35卷第1l期湖南大学学报(自然科学版)

Vbl.35,No.11

2008年11月

JournalofHunanUniversity(NaturalSciences)

Nov.2008

文章编号:1674—2974(2008)1

1-0049.05

用于流水线伽)C的预运放一锁存比较器的分析与设计。

吴笑峰’,刘红侠,石立春,周清军,胡仕刚,匡潜玮

(西安电子科技大学微电子学院,宽禁带半导体材料与器件教育部重点实验室,陕西西安710071)

摘要:提出了一种应用于开关电容流水线模数转换器的CMoS预运放一锁存比较器.该比较器采用UMC混合/射频0.18肛m1P6MP衬底双阱CMOS工艺设计,工作电压为

1.8

V.该比较器的灵敏度为0.215mV,最大失调电压为12mV,差分输入动态范围为1.8

V,分辨率为8位,在40M的工作频率下,功耗仅为24.4ttW.基于0.18gm工艺的仿真结果验证了比较器设计的有效性.

关键词:预运放一锁存比较器;流水线√岫C;踢回噪声;分析与设计

中图分类号:TN432

文献标识码:A

AnalysisandDesignofPre..amplifier..Latch

ComI

Fitting1tt|ngfortor10ipelinePipeline

WU

Xiao-feng*.LIUHong—xia。SHILi—chun。ZHOU

Qing—jun,

HidShi—gang,KUANGQian—wei

(KeyLaboratoryofMinistryofEducationforWideBand.GapSemiconductorMaterialsand

I)ewices,SchoolofMicroelectronics-Xi’anUnivofElectronicScienceandTechnology-Xi’an.Shaanxi

710071.China)

AbstractACMOSpreamplifier-latchparatorusedinswitched??capacitorpipelineanalog??to-digital

con?-

verter

WBSpresented.TheparatorWaSd髑ignedunderUMC

Mixed.Mode/RF0.18btm1P6MP.SubTwin—

WellCMOSprocess

andworked

with1.8Vpowersupply.Thesensitivityoftheparatorwas0.215mV,

thelargestoffsetvoltagewas12mV,thedifferentiaIinputrangeWas1.8V,theresolutionwas8bitandthe

power

dissipationWasonly24.4gWat40MHz.HSPICEsimulationsoftheparatorimplementedin

a

0.18

/_tmtechnologydemonstrateitseffectiveness.

Keywords:pre-amplifier—latchparator,pipelineADC,kick?back

noise,analysisanddesign

比较器是模拟集成电路中的一个基本而重要的速度和功耗的要求比较严格,特别是在高速高分辨模块,被广泛应用于模数(~D)和数模(D/A)转换器率PipelineADC中.

中.衡量应用于~D转换器中的比较器的重要性能目前,应用于PipelineADC中的比较器的主要指标主要有工作速度、功耗、灵敏度、输入失调电压、结构有静态锁存比较器一。,甲乙类锁存比较器。6。和踢回噪声(Kick.backNoise)和输入动态范围等㈠2|.动态锁存比较器‘7].其中,静态锁存比较器中的预运通常,就应用于流水线模拟/数字转换器ADC(Am—

放和锁存器,不论在预放大阶段和再生阶段都有静logtoDigital

Convert)门一。中的比较器而言,由于该

态电流,功耗较大;而且信号路径上有2个极点,降类ADC的后端采用了数字纠错DC(Digital

Corree.

低了比较器的速度,但同时也减小了踢回噪声.甲乙tion)电路,对输入失调电压的要求相对降低.但对

类锁存比较器通常由预运放和甲乙类锁存器构成,

?收稿日期:2008-02—16

基金项目:囤家自然科学基金资助项目(60206006)和国防预研基金资助项目(51308040103)及西安应用材料创新基金资助项目(xA—

AM一200701)

作者简介:吴笑峰(1974~).男,湖南涟源人,西安电子科技大学博士研究生十通i代联系人.E.mail:wiIlow_wxf@hotmail.∞m

湖南大学学报(自然科学版)2008年

该锁存器只在再生阶段有动态电流,而预运放在预放大阶段和再生阶段都有静态电流,因此,这类比较器的整体功耗较静态锁存比较器小.此外,这种类型的比较器的预运放输出端直接连接到再生节点,虽然速度快,但踢回噪声仍较大.动态锁存比较器没有使用预运放,且锁存器只在再生阶段有动态电流,因而其功耗是3种结构中最小的,但失调电压和踢回噪声最大.本文提出了一种新颖的预运放一锁存比较器结构,该比较器属于改进型甲乙类锁存比较器,且对该比较器进行了理论分析和优化设计,并且合理地选择了踢回噪声减小技术,所设计的比较器能够以较高速度工作,踢回噪声小,具有高灵敏度和低功耗的特点.

1

电路描述与工作原理

图1(a)一(c)给出了本文提出的预运放一锁存

比较器的电路结构.图中的开关除S5、S6、SIO、S14和S17采用NMOS开关外,其他都采用CMOS开关.图l(a)为2个开关电容参考电压产生电路,对于图1(a)左端的电路,该参考电压产生电路给出的参考电压为0.对于图1(a)右端的电路。8j,可得

Vxp—Vo=(VⅥ尸一VⅥN)一

1

寺(V矿耐p—Vv耐。).

一

(1)

这表明该参考电压产生电路给出的参考电压为

V,a]4,V一=V嘣d—Vl,。h.

奸

VCM

V

VCMG

VCM

XN

%一‰2‰P-‰

S16

%一‰=(v‰)一}(_砷一K。)

0PON

(b)(c)

图1提出的预运放一锁存比较器的电路结构

Fig.1

Proposed

preamplifierlatchparatordrcuitdiagram

第11期吴笑蜂等:用于流水线ADC的预运放一锬存比较器的分析与设计

51

图l(b)为预运放电路.图中,NMOS管M1和M2构成差分对。M7和姻构成电流源管.其中,M8工作

在饱和区,M7工作在线性区.PlVlC8管M3和M4构成二极管连接的负载,稳定预运放的输出共模电压.这种结构的预运放具有良好的线性,但增益较低.因此,采用PMOS管M5和M6构成交叉耦合的负载,用来提高预运放的增益一。.NlVK)S管MCl和MC2构成/VlOS电容用来减小踢回噪声¨….

图1(c)为锁存器与输出缓冲电路.卜M∞管M9

和MIO构成差分对,M17为电流源管.Mll,M13和M12,M14构成了2个交叉耦合的反相器形成正反馈。M15,M16为预充电管,它们用来复位比较器;反相器INVl与INV3和INV2与INV4分别为比较器输出端Q与O.13的缓冲器,它们对锁存器的输出信号进行整形,同时提高比较器的驱动能力.开关S17在比较器的保持阶段给N移和M10栅极寄生电容上的电荷提供泄敖路径,以免干扰本次比较,这是本文提出的用于提高

比较器灵敏度的关键措施.

比较器的工作过程分为3个阶段:保持阶段、复位阶段和再生阶段.当P1为高电平时,比较器参考电压产生电路的2个输出端电压均为v、,Ⅲ;,它们为预运放提供输入共模电平.预运放的2个输出端电压相等,并为锁存器输入差分对提供共模电平;此时,P2PB为高电平,锁存器电流源管M17导通,差分对管M9,M10也导通,为M11,M13以及M12,M14两个交叉耦合的反相器提供直流通路,而预充电管M15,M16截止,比较器的输出端保持原来的状态.此时,由于开关S17的闭合,上次比较过程中存储在锁存器输入差分对管的栅极寄生电容上的电荷被释放,为本次比较做好准备,这有效地提高了比较器的灵敏度.以图1(a)中右图为例,当P2为高电平时,比较器参考电压产生电路的输出为比较器的差分输人电压与系统差分参考电压之差,这个电压差经预运放放大后提供给锁存器的差分对.由于此时P2PB为低电平,锁存器电流源管M17截止,预运放输出端提供的电压差给锁存器差分对M9,M10栅极的寄生电容充电,为再生阶段提供初始压差.这时。预充电管M15,M16导通,交叉耦合反相器的输出端均为高电平,经2个反相器反相后,比较器的输出端Q和QB均为高电平,比较器被复位.当P2P变为低电平时,P2PB变为高电平,M15,M16截止,M17导通.由于M9,M10栅极的初始压差,差分对中的一个管子给它漏极所连接的反相器中的N管提供较多的电流,使得该反相器输出端负载电容放

电速度较快,并由于正反馈的作用,交叉耦合反相器的输出端快速建立起相应的判决电平,该电平经2个反相器整形后输出最终的比较结果,这是再生阶段.当Pl再次变为高电平后,比较器又一次进入保持状态.

2电路的优化设计

2.1速度、灵敏度、功耗与踢回噪声

提高比较器速度的主要方法有13j:增大预运放的增益;降低预运放的时间常数;降低锁存器的时间常数.图2给出了预运放交流小信号等效电路图。

斗啷杠ii善兰椤畔≥

图2预运放交流小信号等效电路图Fig.2

PreamplifierAC同mllsignalequivalent

circuit

在该电路中,g。l=g碰,g,,f3=g。4,g脚=g舶,

C删=G卿.由图可得预运放的传输函数为:

半(s)=上g,,3-g,,5+SCxoN=

gmI

g们卜丛+鱼堕。

(2)

gm3

g.u3

从上式可以看出,只要g,西小于编加预运放的极点就在左半S平面,系统将是稳定的.预运放的直流增益为:

导≯㈦卜i彘=

g。I

l

(3)

g郴1一垒堕

譬m,

显然,由于添加了交叉耦合负载M5,M6,预运放的

增益提升了‰3/(g,,13一g硝)倍,只要调整M5,M6

与M3,M4的宽长比,即调整g。5与g椰之比,就可方便地调整增益提升量.

从式(2)还可以看出,预运放的时间常数为G川/(g莉一g柑).降低预运放的tt,-Jf日-]常数需要减小预运放输出端的电容,同时合理选择差分对的偏置电流并适当提高g小与g-m的差.在本文提出的比较器里,预运放的所有管子都尽量取较小沟道长度,在兼顾增益的情况下减小输出端寄生电容.为提高灵敏度,考虑到本文所设计的比较器的再生节点和预

52

湖南大学学报(自然科学版)2008矩

运放的输入端被M13,M14以及锁存器的差分对M9.M10隔离,踢回噪声不是很大,因而只采用了中和技术来减小踢回噪声.中和电容的加入在一定程度上减小了比较器的工作速度,但对灵敏度不会有明显的影响.

锁存器的工作速度与交叉耦合反相器在再生阶段开始时的跨导、M9,M10的跨导和电流源管M17所能提供的电流呈正相关,且与锁存器的负载电容呈负相关H1i.增加M9,MIO的跨导和M17的电流能有效地提高锁存器的工作速度,同时也意味着功耗的增加.此外,从比较器的工作过程可以看出,预运放在整个过程中都存在静态电流,而锁存器在保持阶段存在静态电流,在再生阶段存在动态电流,而在复位阶段无功耗.这3个阶段中,保持阶段和复位阶段占比较器整个工作过程的大部分时间段.因此,在保证工作速度和灵敏度的前提下合理地选取预运放的尾电流和锁存器尾电流源管M17的尺寸是降低本文设计比较器的关键.经理论分析和HSPICE

仿真优化,预运放的尾电流为15衅;锁存器尾电流

源管M17的尺寸为(3删0.18脚)×2.

2.2失调电压

预运放一锁存比较器的失调电压主要来源于预运放的失调电压,因为锁存器产生的失调电压在等效到比较器输人端时被预运放衰减,可以忽略不计.因此,本文中比较器失调电压的标准差近似为:

盯2僵≈口i.2+仃j.5+盯42.6=盯i.2+2仃;.5.

(4)

其中,

盯j.2_铬+(半×瓮),^2

Tr2

^2

d≯罴[韶+(半×瓮)].

式中,口;.。是预运放输入差分对失调电压的标准差;

盯;.,是预运放负载管失调电压的标准差;A蜊,

Am,A创,A酽分别是N管和P管工艺模型中阈值

电压的失配因子和电流失配因子.从式(3)可以看出,减小预运放输入差分对管和负载管的过驱动电压,并适当增加它们的面积可有效地减小输入失调

电.压.

3仿真结果及分析

通过以上的分析,对本文提出的预运放一锁存比较器在UMC混合/射频0.18胛1P6M

P衬底双

阱CMOS工艺条件下,采用HSPICE的仿真与优化,最终确定比较器的核心电路(预运放与锁存器)

内各晶体管尺寸如表1所示.

表l

比较器核心电路各晶体管尺寸

Tab.1

Transistorsireof

cole

parator

晶体管

w/l。(肛m/12m)x

m

品体管

w/L(t,m/[tm)xill

M1.M2(410.2)×4M11,M12(2/o.18)×1

M3,M4

(1.6/0.4)×1M13,M14(I/0.18)×1

M5,M6

(1.310.4)×lM15,M16

(0.44/0.2)X1M7(2/1)×3M17(3/0.18)×2M8(5/0.5)×3

MCl,MC2

(4/0.2)×2

M9,M10

(2/0.3)×2

仿真条件如下:时钟信号频率40Mq-Iz;电源电压1.8V;温度125℃;工艺角SS;ADC系统共模电

压V删为0.75V;预运放输入共模电压V删为0.9V;预运放尾电流源电流15衅;比较器输入差

分电压0.215mV,信号源内阻为4(用于踢回噪声的测试);比较器输出端负载0.1pF;参考电压产生电路采用图l(a)左端的结构.比较器的性能指标仿真结果如表2所示.

表2

比较器的性能指标仿真结果

Tab.2

Simulatedresultofperformanceoftheparator测射参数

仿真结果

电源电压

1.8V功耗24.4ttW@1.8v@40MHzT作频率40MHz

输入失调电JK的分布范围

22mV输入灵敏度0.215mV比较精度8位

鱼△皇堡堕国圭l:§Y

图3给出了在比较器的保持阶段,加入复位开关S17前、后比较器中锁存器输入端差分电压的波形.该图中,虚线和点划线分别表示加人复位开关前、后的情况.从图中可以看出,加入复位开关前,在上个比较周期时存储在比较器中锁存器的差分对的栅极寄生电容上的电荷得不到泄放,它干扰了本次比较,以至输出错误的结果.这种情况多发生在上次比较周期时比较器差分输入电压较大,而本次比较周期时,差分输入电压较小的条件下.在加入复位开关S17后,上述问题得到了解决,比较器的灵敏度得以提高.

图4分别用虚线和点划线给出了在加人中和电容前、后踢回噪声的情况.在同一时间点67.631

r15

处,比较器输入差分电压、,旷V州为215.05

ttV;

加入中和电容前比较器的预运放输入端的差分电压

%.‰为126.13肛V;加人中和电容后比较器的预运放输入端的差分电压VxF‰为190.74弘V.这

说明由于踢回噪声的影响,预运放输入端的差分电压与比较器输入端差分电压相差较大,因此,可以认为踢回噪声降低了比较器的灵敏度.但是,在加人中

第11期

吴笑峰等:用于流水线ADC的预运放一锁存比较器的分析与设计

53

和电容MCl和MC2后,这种灵敏度的降低可以忽略不计.而且,在加人中和电容后,踢回噪声的峰值由1.185mV左右(1.4mV~0.215mV)降到了

0.64

的极性发生了改变(它与差分输入信号的极性相同).这表明使用中和电容能有效地减小踢回噪声,提高比较器的灵敏度,并保证比较器输出结果的正确性.

‘”:t‘哪

■∞,■q_卜—b呻I-咐

mV左右(0.855

mV~0.215

mV),且踢回噪声

“O,●∞哪棚,棚●呻'

O5

≯

O。,o5O5O5

》

O

日n:t钟

o曲

505l

图3锁存器输入端在加入复位开关S17前、后的瞬态波形对比

Fig.3

CcIfIlparisionsoftransientwaveforllk,5ofinputof

thelatchwithandwithout

res,et

switchS17

Fig.4

图4加入中和电容前、后踢回噪声的情况对比

Comparisionsofkickbacknoisewithandwithoutneutralization

capacitance

4结论

[4]

200一MS/sCMOS阳rallelpipelineA/Dmnverter[J].IEEEJ

Solid—StateCircuits,2001.36(7):】048一1055.

WALTARIM.HAIDNENK.1一V.9一Bitpipelinedswitched—opamp(1):129—134.

本文提出的预运放一锁存比较器属于改进型甲乙类预运放一锁存比较器.通过对其速度、灵敏度、功耗、踢回噪声和失调电压的优化设计,使该比较器在较高工作速度的情况下仍具有低功耗、高灵敏度和低踢回噪声的特点.此比较器已经应用于40

MFIzPipelineADC的设计中,同时它也可应用于Sigma.DeltaADC中.

[8][6][5]

ADC【JJ.1EEEJSolid.StateCircuits,2001.36

re.

SONGB.LEE

S.TO~鹏盯M.A10—b15一MHzCMOS

cyclingtwo-step~Dconverter[JJ.IEEEJSolid—StateCircuits,

】990,25(6):1328一1338.

UYTTENHoV}’K,SrEYAERTM.A1.8V6一bit1.3一GHzfl&shADCin0.25,tanCMOSlJ].IEEEJSolid.StateCir—culls,2003,38(7):1115一1122.

PEI)R0M.FIGUEIREDO.JOA0C.vital16ckbacknoisere.ductiontechniqu∞forcM(焉Iatchedcornpa.rators[J].IEEETratl.sOnCircuitsandSystenlsll,2006。53(7):541—545.

[7]

AB()ANDREWM,PAULR(j.A1.5V,10—bit,14.3一Ms『scMOSpipelineanalog—to-digitalconverter[J].IEEEJSolid.

SlateCircuits,1999,34(5):599—606.

HAMADEAR.AsinglechipAII—MOS8-bitA/Dcmvener[J】.IEEEJS0lid.StateCircuits.1978.13(6):785—791.

GRAYPR,HURS'TPJ.Analysisanddesignofanalogintegrated

参考文献

[1]

[9】【10]

SU^4A她N

L,WALTARIM,HAKl0、RAINENV.CMOS

dynarnlcparatorsforpipelineA/Dconveners[C]//IEEE

I义AS,2()02,5:157—160[2]

EIJJSHIRAI.CM(YSmultistagepreamplifierdesignforhigh.,speedandhigh—m-solutionparators[JJ.IEEETransCircandSyst.1I:Exprc.NsBriefs.2007,54(2):166—170.

SUMANENL,WALTARIM,HALONENKAI.A10一bit

circuits【MJ.NewYork:JohnWiley&Sons111c。200l:849—

850.

[3]

WICHTB,NIRS(’HIT.S(WIMIr『-LA.M38IEDELD.Yieldand.speedoptimizationoflatch?typeamplifier[J].IEEEJ!bbd—StateCircuits。2【m4,39(7):1148一1158.

voltage耀m

范文四:protel 窗口比较器设计

课程设计任务书

学生姓名: 专业班级: 指导教师: 工作单位: 题 目: Protel的窗口比较器设计 初始条件:

1. Protel软件;

2. 先修课程:电路原理等;

要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)

1、熟悉Protel软件及其应用环境,在电脑上安装该软件;

2、完成电路图的设计、电路的仿真、网表的打印、自动布线印制版图、对自动布线的结果进行手动布线、元器件清单的打印;

3、独立完成课程设计说明书,课程设计说明书按学校统一规范来撰写,

具体包括:

(1) 目录; (2) 理论分析; (3) 程序运行结果及图表分析和总结; (4) 课程设计的心得体会; (5) 参考文献(不少于5篇)。

时间安排:

周一、周二查阅资料,了解设计内容;

周三、周四程序设计,上机调试程序; 周五、整理实验结果,撰写课程设计说明书。

指导教师签名: 年 月 日 系主任(或责任教师)签名: 年 月 日

目 录

摘要 ................................................................................................................................ I

1 Protel简介 ....................................................................................................1 2 电压比较器 ..................................................................................................2 2.1 电压比较器的功能 ...........................................................................................2

2.2 运算放大器的工作状态 .....................................................................2 2.3 电压比较器的类型 .............................................................................2

2.4 电压比较器的性能指标 ...................................................................................2 3 窗口比较器 ................................................................................................................ 3

4 电路原理图设计 ..........................................................................................5

4.1 创建新项目 .......................................................................................................5

4.2 放置元件. ............................................................................................6 4.3 原理图布线 .........................................................................................7

4.4 编辑和调整 .......................................................................................................8

4.5 ERC检查(电气规则检查) .............................................................9 4.6 生成网络表 .......................................................................................10

4.7 元器件清单的生成 .......................................................................................10

5 用Protel 进行PCB印制版图的制作...................................................... 11

5.1 创建PCB文件 ................................................................................. 11

5.2 加载网络表 ..................................................................................................... 11 5.3 元器件布局 .....................................................................................................12 5.4 自动布线 .........................................................................................................12 5.5 编辑和调整 .....................................................................................................13

5.6 铺地 ...................................................................................................14

6 设计总结 ..................................................................................................................16 7 课程设计心得体会 ..................................................................................................17 参考文献 ......................................................................................................................18 附录1 ...........................................................................................................................19

摘 要

本课设是基于的窗口比较器设计。理论部分,首先讲述了Protel简介,再总的讲解了电压比较器的几个相关问题,最后主要详细地进行了窗口比较器的理论分析。对窗口比较器的Protel制作主要进行了电路原理图设计,网表的打印、PCB印制版图的制作、元器件清单的打印这几个流程。

关键词:Protel 电压比较器 窗口比较器 原理图 网络表 PCB 元器件清单

1 Protel简介

Protel是澳大利亚Protel Technology公司推出的一个全32位的电路板设计软件。该软件功能强大,人机界面友好,易学易用,使用该软件的设计者可以容易地设计出电路原理图和画出元件设计电路板图。而且由于其高度的集成性与扩展性,一经推出,立即为广大用户所接受,很快就成为世界PC平台上最流行的电子设计自动化软件,并成为新一代电气原理图工业标准。

Protel主要有两大部分组成,每一部分个有几个模块。第一部分是电路设计部分,主要有:原理图设计系统,包括用于设计原理图的原理图编辑器Sch,用于修改和生成原理图元件的元件编辑器,以及各种报表的生成器Schlib。印刷电路板设计系统,包括用于设计电路板的电路板编辑器PCB以及用于修改,生成元件封装的元件封装编辑器PCBLib。第二部分是电路仿真与可编程逻辑器件设计,主要有:电路仿真系统,包括一个功能强大的数/模混合信号电路仿真器,能在原理图基础上进行连续的模拟信号和数字信号仿真。可编程逻辑器件设计,包括一个文本编辑器,用于编译和仿真设计结果的PLD设计以及观察仿真结果的波形。

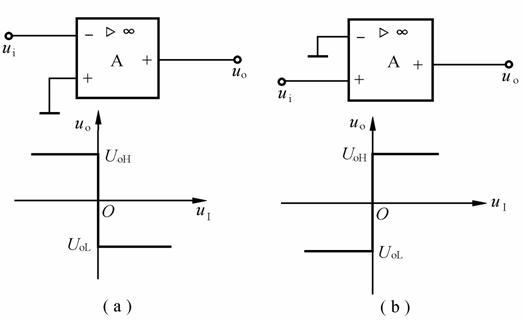

电压比较器是用以比较两个电压大小、即输入电压信号和一个参考电压大小,并用输出高电平VOH和低电平VOL表示比较结果。电压比较器常常用于将任意波形转换成方波或者用于波形整形,在信号的测量、自动控制系统、信号处理和波形产生中得到了广泛的应用。常用的电压比较器有单门限电压比较器、迟滞电压比较器、窗口比较器等。这里主要介绍窗口比较器。

集成运算放大器有线性工作区和非线性工作区两个工作区。运算电路使用的是运算放大器的线性工作区,电压比较器使用的是运算放大器的非线性工作区。

2.1电压比较器的功能

电压比较器是用来比较两个电压大小的电路,它的输入信号时模拟电压,输出信号一般只有高电平和低电平两个稳定状态的电压。利用电压比较器可以将各种周期信号转换成矩形波。

2.2运算放大器的工作状态

电压比较器电路中的运算放大器一般在开环或正反馈条件下工作,运算放大器的输出电压只有正和负两种饱和值,即运算放大器工作在飞线性状态下。这种情况下,运算放大器输入端“虚短”的结论不再适用,但是“虚断”的结论依然适用(由于运算放大器的输入电阻很大)。

2.3电压比较器的类型

常用的电压比较器有零电平比较器、非零电平比较器、迟滞比较器和窗口比较器等电路。零电平和非零电平比较器只有一个阀值电压,称为单门限比较器。迟滞比较器和窗口比较器有两个阀值电压,称为多门限比较器。

2.4电压比较器的性能指标

(1)阀值电压:比较器输出发生跳变时的输入电压,称为阀值电或门限电平Vth 。 (2)输出电平:输出电压 为高电平VOH和低电平VOL。

(3)回差电压:迟滞比较器两个阀值电压(正向阀值和反向阀值)之差 VT

如果希望检测vi是否在给定的两个电压之间时就可以采用窗口比较器。窗口比较器的特点是vi沿着一个方向变化时,可以使v0产生两次跳变。

图3-1 窗口比较器电路图

图3-2 窗口比较器的传输特性

窗口比较器的电路图如图3-1所示,电路由两个幅度比较器和一些二极管与电阻构成,D1和D2是输入保护二极管,D3和D4的作用是防止电流回流损坏运算放大器。将参考电压VH加于放大器A1的反向端,VL加于放大器A2的反向端,且有

VH=VL+2VD

将输入信号vi输入到运算放大器的同相输入端,这是运算放大器处于开环工作状态,具有很高的开环增益。由于受到正相电源电压、二极管和电阻的限制,输出电压为+Vom或者0。

设R1=R2,二极管的正向导通电压为VD,则有

VL=

(VCC-2VD)R2

R1+R2

=

12

(VCC-2VD)

VH=VL+2VD

电压传输特性曲线是反映输出电压v0和输入电压vi之间关系的曲线。窗口比较器的电压传输特性如图3-2所示。输入信号偏离参考电压时,输出电压将发生跃变。由图可见 当vi>VH时,v01为高电平,D3导通,v02为低电平,D4截止,v0=v01; 当vi<>

当VL<>

4电路原理图设计

电路原理图的设计是整个电路设计的基础,因此电路原理图要设计好,以免影响后面的设计工作。电路原理图的设计包括创建新项目、放置元件、原理图布线、编辑与调整、ERC检查(电气规则检查)、生成网络表。

4.1 创建新项目

进入Protel界面,执行菜单File命令创建一个新项目(项目中包含所要设计的文件),弹出如下对话框,在对话框的Design Storage Type选项中选择默认值,在Database file name

后添加项目的名称“刘小燕”.ddb,其扩展名必须以ddb结尾。通过按Browse按钮指出将文件存储于E盘。最后点击OK键,则建立了一个项目,弹出以下的对话框中选择原理图服务器(Schematic Document)图标,双击该图标建立原图设计文件Sheet1.ddb。双击该图标进入原理图设计主界面。执行菜单Design/OptionsTool/Preferences,设置图纸大小、捕捉栅格、电气栅格等。

4.2 放置元件

在设计管理器中选择Browse Sch页面,如下图所示,在Browse区域中的下拉框中选择Library,然后单击Add/Remove按钮,在弹出的窗口中寻找Protel 子目录,在该目录中选择Library/Sch路径,在元件库列表中选择所需的元件库,比如Miscellaneous Devices lib,TI Databook库等,单击Add按钮,即可把元件库增加到元件库管理器中。

根据设计窗口比较器的需要,先从元件库Miscellaneous Devices lib中找到OPAMP,从元件的外行可以看出这正是我们要找的放大器,然后用鼠标点击Place按钮,即可将该元件移动到设计图纸中。按同样的操作再移入另一个放大器。然后继续在这个元件库中找到DIODE,此即我们要找的二极管,然后用鼠标点击Place按钮放入四个二极管。然后再在Digital Objects工具条中选择3个电阻(单击鼠标左键即可得到元件,然后再在工作区中单击鼠标左键即可把元件放入设计图纸。)。最后在电源实体Power Objects中选择接地符号放入原理图纸中,重复放入五个。

在摆放的过程中,可以通过键盘上的SPACE、X、Y三种键来改变元件的放置位置,其中SPACE键是让元件作90°的旋转,X键使元件左右对调,即以自光标为轴作水平对调,Y键使元件上下对调,即以自光标为轴作垂直对调,再根据元件之间的走线把元件调整好。

4.3 原理图布线

利用Protel

提供的连线工具条中的连线工具

进行连线(只有此线才是具有电气性

质),当预拉线的指针移动到元件的引脚或者其他电气特性线时,指针的中心就会出现一个黑点,它提示我们在当前的状态下单击鼠标左键就会形成一个有效的电气连接。这里需要注意的是,连线不能贯穿元件(若连线贯穿元件会造成PCB制作中元件也是短路的,仿真环节无法正确通过),连接线段不能重合(若连接线段重合会造成PCB制作环节中加载网络表后出现短线),元件不能搭接(如果元件搭接点在元件端口之内,程序无法识别也会造成PCB制作环节中加载网络表后出现短线)。

连接好后,再放置输入/输出端口。在Writing Tools

中选择放置在电路的输入端口。双击输入端口,则弹出以下对话框,在弹出的对话框中的Name中键入Vi,在Style 中选

择Right,在I/O Type 中选择Input,在Alianment中选择Right,其他的选择默认,点击OK键即设好了输入端口的属性。再在输出放置一个输出端口,双击该图标,在弹出的对话框中的Name中键入Vo,在Style 中选择Right,在I/O Type 中选择Output,在Alianment

中选择Right,其他的选择默认,点击OK键即设好了输出端口的属性。

4.4编辑和调整

利用Protel 所提供的各种强大的功能对原理图进一步调整和修改,以保证原理图的美观和正确。同时对元件的编号、封装进行定义和设定,更改元件属性等。

用鼠标双击任何一个元件都会弹出元件的属性对话框,如下图为电阻R1的属性对话框,其中Lib Ref:元件样本,修改此项将直接替换原有的元件,元件样本名不会显示在元件图上;Footprint:元件的封装方式,元件的封装是指设计PCB时,根据实际元件尺而定义的焊点,另外还附加一些属性和元件外观的符号,需要注意的是每个元件的Footprint必须要添上相应的封装号(这里电阻的封装号:AXIAL0.3,二极管:DIODE0.4,放大器:

DIP8)Designator:设置元件的序号;Part Type:设置元件参数值如电阻的大小,电容的电容值等(这里R1:1K,R2:1K,RL:2K)。

4.5 ERC检查(电气规则检查)

当整个电路设计完成后,可以进行ERC检查。主要是检查电路图中是否有电气性质不一致的情况(如元件的序列号重复,出现两个RL),ERC检查检查依据问题的严重性分别以错误(Error)或者警告(Warning)信息来提醒用户,下图为窗口比较器的ERC检查。选择TOOLS菜单下的ERC项在弹出的对话框中直接点击OK键即可进行ERC检查,如果有错误则要返回原理图中进行修改,修改完成后在进行ERC检查,直至没有错误为止。

4.6生成网络表

网络表是电路原理图设计和印刷电路板设计之间的桥梁,是PCB中自动布线的灵魂。所以必须生成网络表。

选取Design设计菜单下的Create Netlist选项则会弹出一对话框,在对话框中点击OK就可生成网络表文件Sheet1.NET,附件1所示为所做窗口比较器的网络表。

网络表文件包含两种内容:一对方括号之间表示一个元件的属性,有序号、封装号和参数;一对圆括号之间是通过一个点的连接线,包括从哪点出发,接到哪里。

4.7元器件清单的生成

执行Report/Bill of Material命令,则可生成附件2中的元器件清单

至此,电路图Sheet1.Sch全部完成。图4-1为此次设计的窗口比较器的最终原理图。

图4-1窗口比较器的原理图

5用Protel进行PCB印制版图的制作

电路设计的最终目的是为了设计出电子产品,而电子产品的物理结构是通过印刷电路板来实现的。Protel为设计者提供了一个完整的电路板设计环境,使电路设计更加方便有效。应用Protel设计印刷电路板过程如下:

5.1创建PCB文件

执行菜单File/New命令,在弹出的对话框中选择PCB设计服务器(PCB Document)图标,双击该图标,建立PCB设计文档。双击文档图标,进入PCB设计服务器界面。

此界面同Sch设计主界面相似,但增加了板层标签,用来在设计时快速地选择板层。板层就是电路文件中可分层显示的电路板结构图,不同类板层尤其专用的使用意义。如有些板层可以进行实体铜膜走线,有的板层没有电气性质,纯粹是为了在电路板上标注说明文字。板层的概念很重要,制作PCB时一定要对所用的板层有个清晰的认识。

下面再介绍一些与PCB相关的名词。板框:就是规范自动放置和自动布线功能的合法区域,在此规定的区域内放置元件和布线。飞线:常称之为预拉线,是引入网络表后,布线之前,系统根据网络关系生成的一种虚拟的线,只表示一种连接关系。铜膜走线:简称导线,是实际存在的,用来连接各个焊点,是印刷电路板较重要的部分,印刷电路板的设计都是如何布置导线来进行的。焊点:用来放置焊锡、连接导线和零件的引脚。导孔:连接不同板层间的导线孔。

5.2加载网络表

在设计工作区的板层标签上选择KeepOutLayer(这是一个在闭合板框内支持自动布线的层),然后选择工具条Placement Tools

上的按钮,画边框(边框按系统设定的颜色应是紫色)。此时画的只是一个粗略的边框,虽然没必要太精确,但不能太大。待到布线完成后,再来画精确的边框。

执行菜单Design/Load Nets命令,弹出对话窗口,在窗口单击Browse按钮,再在弹出的窗口中选择电路原理图设计生成的网络表文件窗口比较器.Net,点击OK键,弹出下一级对话框,若对话框中显示有封装错误,则必须返回原理图改正元件的属性,再重新生成网络表,重新加载网络表,才能从根本上解决问题。若没有错误,单击Execute键,元件就会加载到工作区上。如果图中元件重叠到一起,就呈现绿色,这是系统默认的警告颜色。

5.3元器件布局

Protel 既可以进行自动布局也可以进行手工布局,执行菜单命令Tools/Auto Placement/Auto Placer可以自动布局。布局是布线关键性的一步,为了使布局更加合理,多数设计者都采用手工布局方式。

先把重叠的元件拖开(当用鼠标左键点中任何重叠元件时,将弹出小的对话框,表示当前点中的地方重叠了几个元件,选择其中的一个元件进行移动):当移动鼠标到相应的字体上,字体全部变蓝,单击鼠标左键,便可获取一个元件,然后再将其拖走。依据电路的功能及元件的大小,适当的摆放元件。

5.4自动布线

Protel PCB采用世界最先进的无网格、基于形状的对角线自动布线技术,能自动地设计出最佳的自动布线策略。执行菜单命令Auto Routing/All,在弹出的窗口中单击Route all 按钮,程序即对印刷电路板进行自动布线。只要设置有关参数,元件布局合理,自动布线的成功率几乎是100%。自动布线完成后,将弹出布线信息对话框,如下图所示,它指出了布线的相关信息,如布线完成的程度、布了多少线、还有几条没布完、布线所用的时间。

点击OK,则布线完成。若对布线不满意,可在工具下拉菜单上选“撤销布线”,恢复飞线状态后可重新布线。

5.5编辑和调整

边框的修改一定要在KeepOutLayer来修改。自动布线结束后,可能存在一些令人不满意的地方,可以手工调整,把电路板设计得尽善尽美。首先,删除不理想的布线,点击Edit/Delete选项,光标变成十字光标,左键点击要删除的导线即可删除。删除导线后,焊点间以飞线连接,然后选取不同的层如top layer(红线)、bottom layer(蓝线)

,选择来画飞线之间连接的导线,注意同一层内的导线不能交叉,直到将不满意的导线改到满意为止。布线结束后可适当地修改元件参数的位置,使布局看起来更加美观。最后可得到图5-1, 从图纸中可以看出导线分为两种颜色,系统默认上层板的布线为红线,底层线的布线为蓝色。

图5-1 窗口比较器PCB印制版图

5.6 铺地

将设计工作区的板层标签上由KeepOutLayer转至TopLayer

,再选择工具栏上的按钮,将会弹出一对话框,在对话框中的Connect to Net中选择GND,点击OK,鼠标将变成光标,用光标将边框再画一遍,则会得到如图6-2所示的PCB的顶层

图5-2 顶层PCB图

将设计工作区的板层标签上由KeepOutLayer转至BottomLayer,

再选择工具栏上的

按钮,将会弹出一对话框,在对话框中的Connect to Net中选择GND,点击OK,鼠标将变成光标,用光标将边框再画一遍,则会得到如图6-3所示的PCB的顶层

图5-3 底层PCB图

6 设计总结

随着电子工业的飞速发展,电路设计越来越复杂,手工设计越来越难以适应形势发展的需要,Protel以其强大的功能、快捷实用的操作界面及良好的开放性,为设计者提供了现代电子设计手段,使设计者能快捷、准确地设计出满意的电路原理图和印刷电路板,不愧是从事电路设计的一个良好的工具。

通过这次Protel电路设计与制版实验课程设计,让我了解了制作与编辑元件电路原理图元器件库的方法—设计电路原理图的方法—对该电路原理图进行电气规则测试的方法—生成该电路原理图的网络表文件的方法—生成该电路原理图的元器件材料清单列表的方法—制作与修改PCB元件封装的方法—设计PCB图的方法及电路原理图仿真的方法。

7课程设计心得体会

时间很紧,这一周又在忙碌的基调中过去了,经过这周的Protel课程设计,我从原先对Protel的一无所知到现在能够利用它进行一些基本电路的原理图设计和PCB的制作,并且实现电路的仿真,之间的巨大变化着实令人吃惊。但是这种进步来之不易,因为这期间我遇到了很多的困难,发现了很多的问题,正是在解决问题的期间我才慢慢地熟悉了Protel,才慢慢地学会了如何使用这种软件。

通过这次Protel电路设计与制版实验课程设计,让我了解了制作与编辑元件电路原理图元器件库的方法—设计电路原理图的方法—对该电路原理图进行电气规则测试的方法—生成该电路原理图的网络表文件的方法—生成该电路原理图的元器件材料清单列表的方法—制作与修改PCB元件封装的方法—设计PCB图的方法及电路原理图仿真的方法。

课程设计是我这学期最忙的日子,期间面临着繁重的考试,这段时间的任务对我来说实在是繁重,因为没有设计经验,更没有Protel的相关基础知识,我只能自己一个人慢慢地摸索,慢慢找到路子,遇到不懂的就大家一起讨论,正是在不断的摸索与探讨中我才在实践中学到了很多东西。

课设的这段日子真的是给我留下了很深的印象。我总结出,在每次课设中,遇到问题最好的办法就是请教别人,因为每个人掌握的情况都不一样,一个人不可能做到处处都懂,必须发挥群众的力量,复杂的事情才能够简单化。这一点我深有体会,在很多时候,我遇到的困难或许别人之前就遇到过,向他们请教远比自己在那边摸索来得简单,来得快。

虽然我现在已经初步学会了如何使用Protel的使用方法了,但是离真正掌握它还有一段的距离。课设的这段时间我确实受益匪浅,不仅是因为它发生在特别的实践,更重要的是我的专业知识又有了很大的进步,进步总是让人快乐的。

参考文献

[1] 吴友宇主编. 模拟电子技术基础. 第一版. 清华大学出版社, 2009年5月

[2] 邱关源主编. 电路. 第五版. 高等教育出版社,2006年5月

[3] 柴靖主编. 中文版Word 2003实用教程. 清华大学出版社,2008年6月

[4] 零点工作室主编. 精通 Protel DXP 2004 电路设计.电子工业出版社,2006年8月

[5] 谈世哲主编. Protel DXP 2004电路设计基础与典型范例. 电子工业出版社,2007年

[6] 刘刚等主编. Protel DXP 2004 SP2原理图与PCB设计. 电子工业出版社,2007年6月

[7] 张阳天、 韩异凡主编. Protel DXP电路设计. 清华大学出版社,2005年6月

附录1:

网络表

[

A1

DIP8

OPAMP

]

[

A2

DIP8

OPAMP

]

[

D1

DIODE0.4

IN4001

]

[

D2

DIODE0.4

IN4001

]

[

D3

DIODE0.4

IN4001

]

[

DIODE0.4

IN4001

]

[

R1

AXIAL0.3

1K

]

[

R2

AXIAL0.3

1K

]

[

RL

AXIAL0.3

2K

]

(

GND

R2-1

RL-1

)

(

NetA1_3

A1-3

D3-A

)

(

NetA2_3

A2-3

D4-A

(

NetD1_K

A1-2

A2-1

D1-K

D2-A

)

(

NetD3_K

D3-K

D4-K

RL-2

)

(

VCC

R1-2

)

(

VH

A1-1

D1-A

R1-1

)

(

VL

A2-2

D2-K

R2-2

)

附录2:

元器件清单

范文五:比较器电路设计

实 验 报 告

课程名称 FPGA 实验项目 比较器 实验仪器 Quartus 2

系 别

专 业

班级/学号

学生姓名

实验日期

成 绩

指导教师

实验二 组合逻辑电路的设计

一、 实验目的

1(设计8段译码器、两路4位二进制比较器,并在实验装置上验证所设计的电

路;

2(学习用AHDL语句进行逻辑描述。

二、实验要求

用AHDL中真值表的设计方法设计8段译码器、用布尔方程的设计方法设计两路4位二进制比较器,对CPLD器件进行配置及下载来验证自己的设计,验证电路的外围器件可选用按键输入、指示灯输出。

8段译码器的逻辑功能

输入 输出

in[3..0] dp g f e d c b a

0 0 0 1 1 1 1 1 1

1 0 0 0 0 0 1 1 0

2 0 1 0 1 1 0 1 1

3 0 1 0 0 1 1 1 1

4 0 1 1 0 0 1 1 0

5 0 1 1 0 1 1 0 1

6 0 1 1 1 1 1 0 1

7 0 0 0 0 0 1 1 1

8 0 1 1 1 1 1 1 1

9 0 1 1 0 1 1 1 1

A 0 1 1 1 0 1 1 1

B 0 1 1 1 1 1 0 0

C 0 0 1 1 1 0 0 1

D 0 1 0 1 1 1 1 0

E 0 1 1 1 1 0 0 1

F 0 1 1 1 0 0 0 1

两路4位二进制比较器逻辑功能

输入 输出

a[3..0] b[3..0] H L E

a[3..0]> b[3..0] 1 0 0

a[3..0]< b[3..0]="" 0="" 1="" 0="">

a[3..0]= b[3..0] 0 0 1

三( 实验代码

--实现4位二进制比较器

library ieee; --库文件

use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity compair4_4 is

port( a:in std_logic_vector(3 downto 0); --定义输入信号

b:in std_logic_vector(3 downto 0);

e,h,i,o:out std_logic --定义输出信号

);

end;

architecture one of compair4_4 is --signal reg:std_logic;

begin

process(a,b)

begin --开始硬件描述

if a>b then e<><><='0'; elsif="" a="b" then=""><><><='0';>

elsif a<><><='1';>

end if;

end process;

--reg<='1';>

--o<=reg;>

o<='1'; --o为141号管脚="">

end;

四(实验截图

软件仿真波形

亦正亦邪26839443

亦正亦邪26839443